# Conception d'un Compresseur de Dynamique en Sigma-Delta

# **Antoine Ricoux**

Mémoire de Master 2 - Spécialité Son

Directeur Interne: Mohammed Elliq

Directeur Externe : Paul Payen de La Garanderie

Responsable Universitaire: Corsin Vogel

Rapporteur: Laurent Millot

Juin 2021

## Résumé:

Ce mémoire explore les moyens théoriques et techniques requis pour créer un compresseur de dynamique audionumérique utilisant la modulation Sigma-Delta ( $\Sigma/\Delta$ ).

Après avoir placé dans son contexte l'utilisation de la modulation Sigma-Delta en audionumérique, comme dans le SA-CD ou dans le DSD, on établira dans la première partie de ce mémoire, la relation entre dynamique et modulation  $\Sigma/\Delta$  à 1 bit. Les enjeux technologiques qui rendent possible la mise en œuvre ce genre de traitement du signal, notamment le recours aux circuits logiques programmable de type FPGA serons également exposés.

Dans la deuxième partie, on présentera le synoptique d'un compresseur audio et l'on expliquera la réalisation de ses sous-blocs en utilisant la modulation  $\Sigma/\Delta$ .

Finalement, on présentera le fonctionnement des outils logiciels et matériels nécessaires à la réalisation de notre compresseur de dynamique en modulation  $\Sigma/\Delta$ . Cette explication sera suivie par la réalisation concrète d'un prototype de compresseur audio en modulation  $\Sigma/\Delta$  utilisant un système sur puce (SoC).

# Mots Clefs:

Sigma-Delta, Compresseur de Dynamique, FPGA, DSD, Traitement Numérique du Signal, Électronique

# Abstract:

This master's thesis explores the theory and techniques required to create a digital audio dynamic compressor for Sigma-Delta modulation. After putting the use of Sigma-Delta modulation in its context, like in the SA-CD and DSD, we establish the relation between one bit audio and dynamics. We also take a look at the technological issues that makes this kind of digital signal processing possible, notably the choice of the FPGA. In the second part, we will explain how every part of a dynamic compressor works and we will suggest a Sigma-Delta schematic for each part.

Finally, we will present the hardware and software tools used for implementing the  $\Sigma/\Delta$  compressor in a system on chip. This presentation will be followed by a concrete implementation of said compressor.

# **Key Words:**

Sigma-Delta, Compressor, FPGA, DSP, DSD, Electronics

### Remerciements:

Je tiens à remercier chaleureusement les personnes dont l'aide précieuse m'a permis d'écrire ce mémoire :

Paul Payen de La Garanderie pour ses conseils avisés et sa disponibilité qui dépassent largement le cadre de directeur externe.

Mohammed Elliq pour sa confiance et son exigence.

Laurent Millot pour ses conseils utiles et son intérêt.

Corsin Vogel pour sa correction express et ses questionnements.

Charleyne, mes parents et ma sœur pour leur patience et leurs encouragements.

William Thenier et Valerian Fraisse pour leurs encouragements.

Florent Fajole pour son accueil au CDI.

Le corps enseignant de l'ENS Louis-Lumière pour un cadre de travail exceptionnel. Enfin, toute la promotion ENSLL Son 2021 pour une camaraderie sans précédent.

# Table des matières

| Ac | rony                                                              | mes                                                                  |                                                                                                                                                                                                                                                                                        | 8                                                        |  |  |  |  |  |  |  |

|----|-------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|

| 1  | Intr                                                              | Introduction                                                         |                                                                                                                                                                                                                                                                                        |                                                          |  |  |  |  |  |  |  |

| 2  | 2.1<br>2.2<br>2.3                                                 | Histo<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>Modu                    | on Sigma-Delta rique & Utilisations Conception de la Modulation Sigma-Delta Super Audio Compact Disc Solutions de Traitement DSD en Temps-Réel 2.1.3.1 DSD-Wide 2.1.3.2 Digital Extreme Definition Évolution du FPGA ulation Sigma-Delta                                               | 12<br>12<br>13<br>15<br>16<br>17<br>18<br>18<br>20<br>21 |  |  |  |  |  |  |  |

| 3  | Traitement Dynamique en Sigma-Delta  3.1 Dynamique en Sigma-Delta |                                                                      |                                                                                                                                                                                                                                                                                        |                                                          |  |  |  |  |  |  |  |

|    | 3.2                                                               | 3.1.2<br>Fonct<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | Calcul de Dynamique                                                                                                                                                                                                                                                                    | 27<br>32<br>32<br>32<br>34<br>34<br>35<br>36             |  |  |  |  |  |  |  |

|    | 3.3                                                               |                                                                      | eption du Compresseur Dynamique Sigma-Delta  Détecteur de Niveau  Section de Commande  Knee: Interpolation du Ratio  Filtre Passe-Bas du Premier Ordre  3.3.4.1 Calcul du Coefficient  3.3.4.2 Temps de Montée  3.3.4.3 Modèle du Filtre  Ligne à Retard du Look-Ahead  Module de Gain | 36<br>42<br>45<br>46<br>48<br>49<br>50<br>52<br>55       |  |  |  |  |  |  |  |

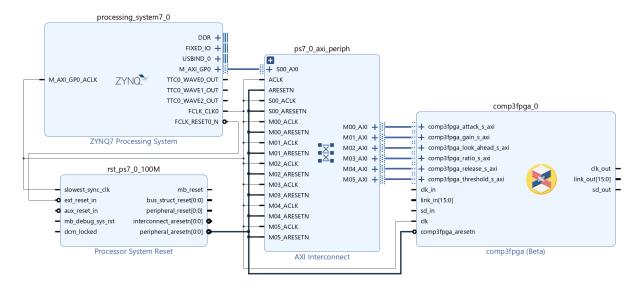

| 4  | Réa                  | Réalisation du Compresseur Sigma-Delta sur SoC 5 |                                                      |    |  |  |  |  |  |  |  |  |  |

|----|----------------------|--------------------------------------------------|------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

|    | 4.1                  | Architecture d'un Système sur Puce               |                                                      |    |  |  |  |  |  |  |  |  |  |

|    |                      | 4.1.1                                            | Architecture de Base d'un FPGA                       | 58 |  |  |  |  |  |  |  |  |  |

|    |                      | 4.1.2                                            | Bloc DSP48E1                                         | 61 |  |  |  |  |  |  |  |  |  |

|    |                      | 4.1.3                                            | Architecture de Base d'un SoC                        | 62 |  |  |  |  |  |  |  |  |  |

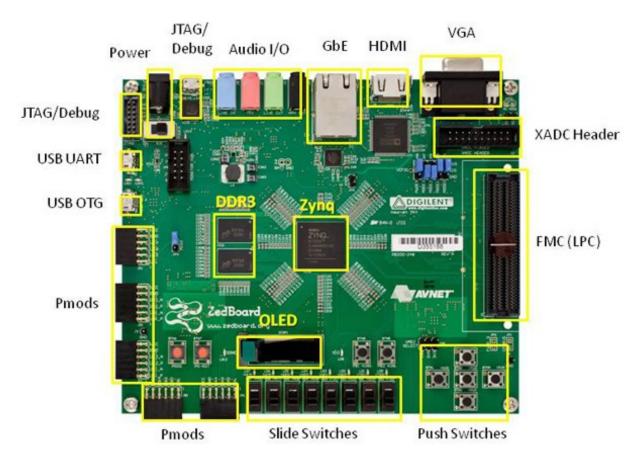

|    | 4.2                  | Présentation de la Chaîne d'Outils               |                                                      |    |  |  |  |  |  |  |  |  |  |

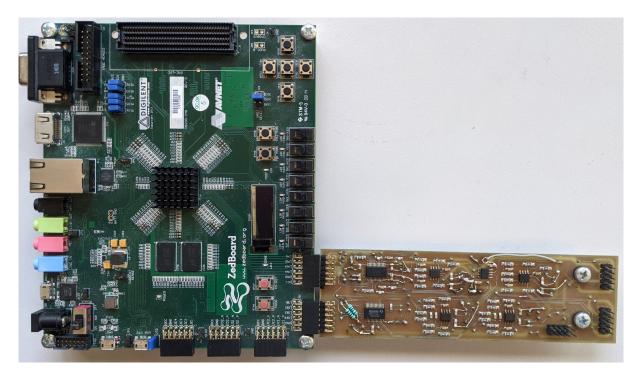

|    |                      | 4.2.1                                            | Plateforme de Développement : Zedboard               | 63 |  |  |  |  |  |  |  |  |  |

|    |                      | 4.2.2                                            | Environnement Xilinx                                 | 64 |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | 4.2.2.1 Vitis & Vivado                               | 64 |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | 4.2.2.2 System Generator for DSP                     | 66 |  |  |  |  |  |  |  |  |  |

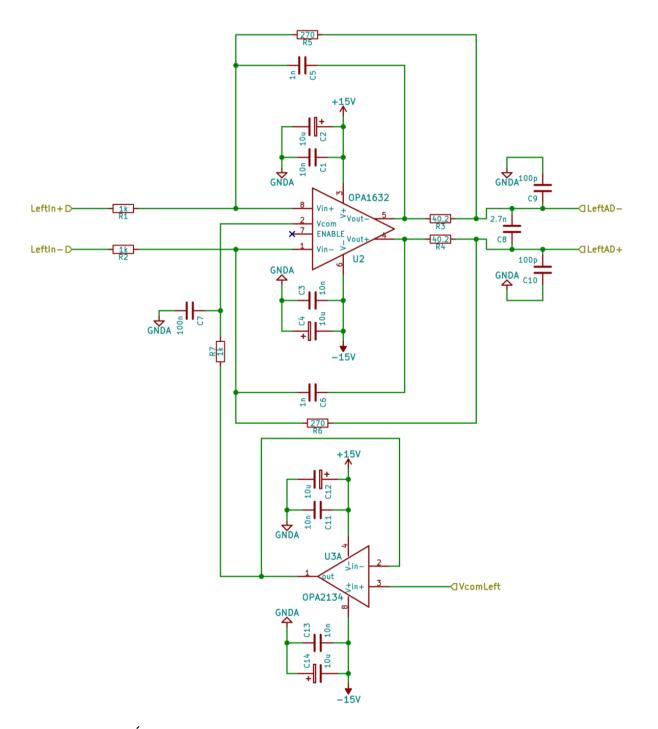

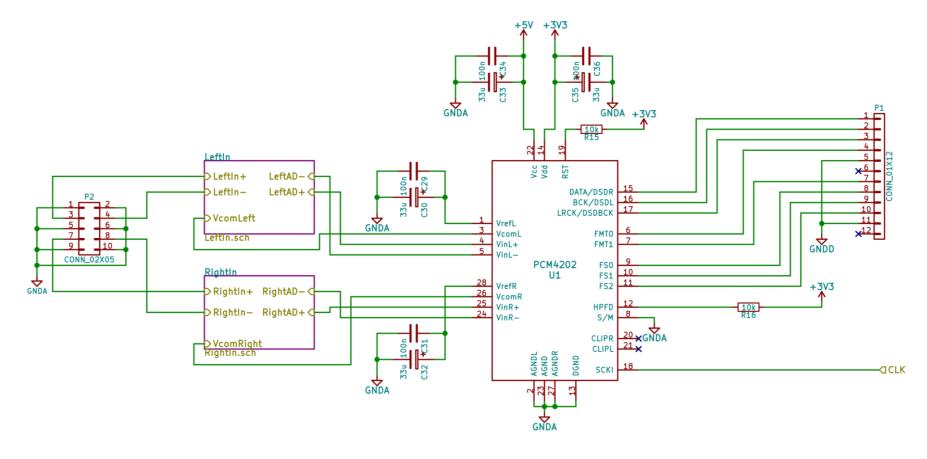

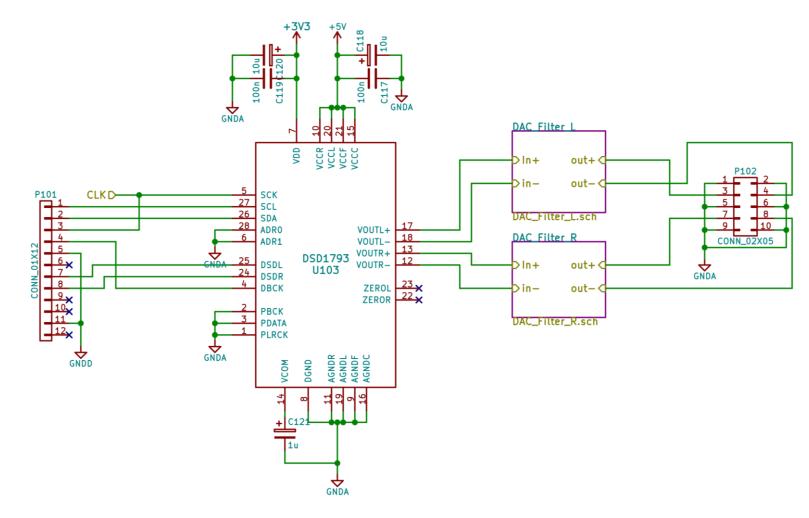

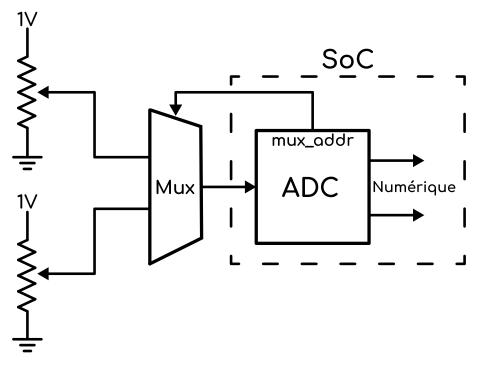

|    | 4.3                  | Circuits de Conversion                           |                                                      |    |  |  |  |  |  |  |  |  |  |

|    |                      | 4.3.1                                            | ADC                                                  | 68 |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | 4.3.1.1 Électronique                                 | 68 |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | 4.3.1.2 Configuration                                | 71 |  |  |  |  |  |  |  |  |  |

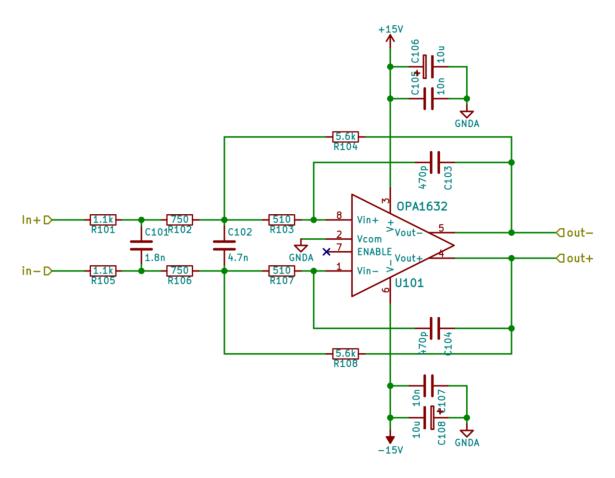

|    |                      | 4.3.2                                            | DAC                                                  | 73 |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | 4.3.2.1 Électronique                                 | 73 |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | 4.3.2.2 Configuration                                | 75 |  |  |  |  |  |  |  |  |  |

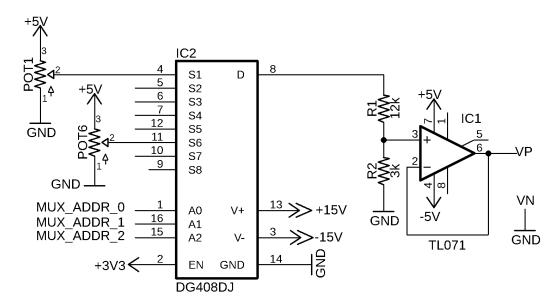

|    | 4.4                  | Interface                                        |                                                      |    |  |  |  |  |  |  |  |  |  |

|    |                      | 4.4.1                                            | Principe du Contrôle du FPGA par le Processeur       | 75 |  |  |  |  |  |  |  |  |  |

|    |                      | 4.4.2                                            | Principe du Contrôle du Processeur par des Potentio- |    |  |  |  |  |  |  |  |  |  |

|    |                      |                                                  | mètres                                               | 77 |  |  |  |  |  |  |  |  |  |

|    |                      | 4.4.3                                            | Indicateur de Réduction de Gain                      | 81 |  |  |  |  |  |  |  |  |  |

|    | 4.5                  | Test du Modèle                                   |                                                      |    |  |  |  |  |  |  |  |  |  |

|    |                      | 4.5.1                                            | Dans Vivado                                          | 84 |  |  |  |  |  |  |  |  |  |

|    |                      | 4.5.2                                            | Mesure Audio                                         | 85 |  |  |  |  |  |  |  |  |  |

| _  | _                    |                                                  |                                                      |    |  |  |  |  |  |  |  |  |  |

| 5  | Cor                  | Conclusion                                       |                                                      |    |  |  |  |  |  |  |  |  |  |

| Ré | fére                 | nces                                             |                                                      | 89 |  |  |  |  |  |  |  |  |  |

| A۲ | pen                  | dices                                            |                                                      | 92 |  |  |  |  |  |  |  |  |  |

| Α  | Fon                  | ctions                                           | de System Generator for DSP                          | 92 |  |  |  |  |  |  |  |  |  |

|    | A.1 System Generator |                                                  |                                                      |    |  |  |  |  |  |  |  |  |  |

|    | A.2                  | Const                                            | tant                                                 | 92 |  |  |  |  |  |  |  |  |  |

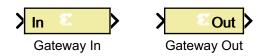

|    |                      |                                                  | vay In/Out                                           | 93 |  |  |  |  |  |  |  |  |  |

|    | A.4 Delay            |                                                  |                                                      |    |  |  |  |  |  |  |  |  |  |

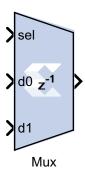

|    | A.5                  | Mux                                              |                                                      | 94 |  |  |  |  |  |  |  |  |  |

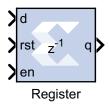

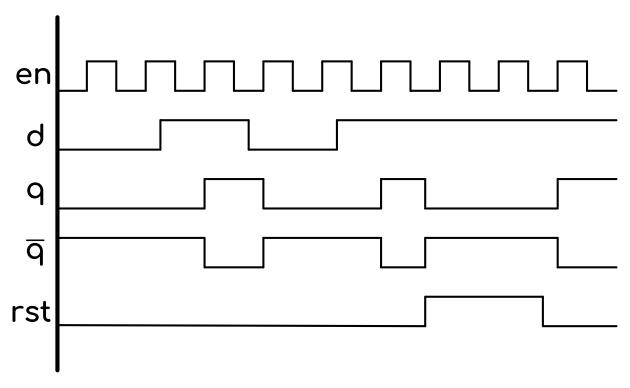

|    | A.6                  | Regist                                           | ter                                                  | 94 |  |  |  |  |  |  |  |  |  |

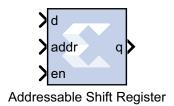

|    | Δ7                   | Addre                                            | essable Shift Register                               | 96 |  |  |  |  |  |  |  |  |  |

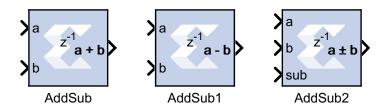

|   | A.8  | AddS              | ub             |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 96  |

|---|------|-------------------|----------------|---------|------|--|--|--|--|--|--|------|------|---|------|-----|

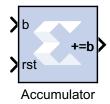

|   | A.9  | Accur             | nulator        |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 97  |

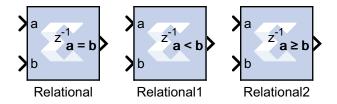

|   | A.10 | A.10 Relational   |                |         |      |  |  |  |  |  |  | 97   |      |   |      |     |

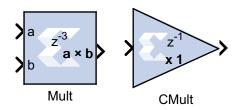

|   | A.11 | Mult              |                |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 98  |

|   | A.12 | Divide            |                |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 98  |

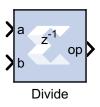

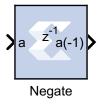

|   | A.13 | Nega <sup>.</sup> | e              |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 98  |

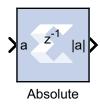

|   | A.14 | Absol             | ute            |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 99  |

|   | A.15 | Conve             | ert            |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 99  |

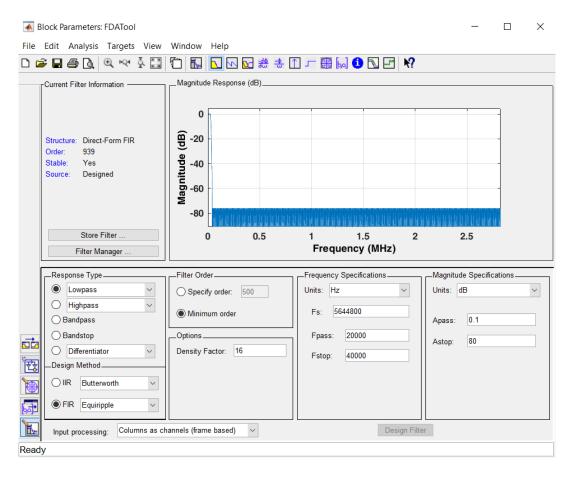

|   | A.16 | Digito            | l FIR Filter 8 | ₹ FDA   | Tool |  |  |  |  |  |  | <br> | <br> |   | <br> | 99  |

|   |      |                   |                |         |      |  |  |  |  |  |  |      |      |   |      |     |

| В | Cald | cul en            | Binaire        |         |      |  |  |  |  |  |  |      |      |   |      | 101 |

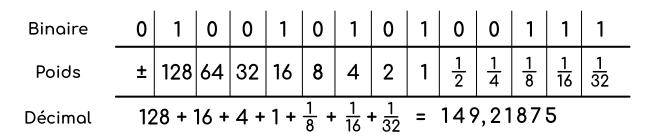

|   | B.1  | Virgu             | e Fixe         |         |      |  |  |  |  |  |  |      |      |   |      |     |

|   |      | B.1.1             | Représento     | ation . |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 101 |

|   |      | B.1.2             | Saturation     |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 102 |

|   |      | B.1.3             | Addition .     |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 103 |

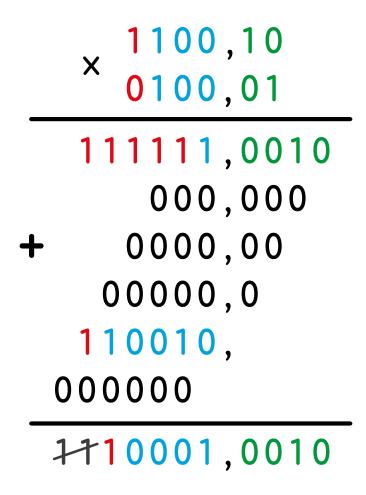

|   |      | B.1.4             | Multiplicat    | ion     |      |  |  |  |  |  |  | <br> | <br> | • | <br> | 103 |

|   | B.2  | Virgu             | e Flottante    |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 104 |

|   |      | B.2.1             | Représento     | ation . |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 104 |

|   |      | B.2.2             | Addition .     |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 106 |

|   |      | B.2.3             | Multiplicat    | ion     |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 107 |

|   | B.3  | Arron             | di             |         |      |  |  |  |  |  |  | <br> | <br> |   | <br> | 107 |

| С | Bus  | I2C               |                |         |      |  |  |  |  |  |  |      |      |   |      | 108 |

| D | Bus  | DSD               |                |         |      |  |  |  |  |  |  |      |      |   |      | 110 |

| Ε | Bus  | AXI               |                |         |      |  |  |  |  |  |  |      |      |   |      | 111 |

Acronymes Antoine Ricoux

# Acronymes

$\Sigma/\Delta$  Sigma-Delta.

$\Sigma/\Delta$ -M Sigma-Delta Modulator.

ADC Analog to Digital Converter.

AMBA Advanced Microcontroller Bus Architecture.

ARM Advanced RISC Machine.

**AXI** Advanced eXtensible Interface.

**CB** Connection Block.

CD-DA Compact Disc - Digital Audio.

DAC Digital to Analog Converter.

**DAW** Digital Audio Workstation.

DBCK DSD Bit Clock.

**DSD** Direct Stream Digital.

**DSDL** DSD Left.

**DSDR** DSD Right.

**DSP** Digital Signal Processor.

**DST** Direct Stream Transfert.

DXD Digital eXtreme Definition.

**EEPROM** Electrically-Erasable Programmable Read-Only Memory.

FIR Finite Impulse Response.

FPGA Field Programmable Gate Array.

**GPIO** General Purpose Input Output.

HDL Hardware Description Language.

**HLS** High Level Synthesis.

I<sup>2</sup>C Inter Integrated Circuit.

IDE Integrated Development Environment.

IEEE Institute of Electrical and Electronics Engineers.

IIR Infinite Impulse Response.

ILA Integrated Logic Analyzer.

IOB Input/Output Block.

IP Intellectual Property.

JTAG Joint Test Action Group.

LB Logic Block.

LED Light-Emitting Diode.

LSB Least Significant Bit.

LUT Look-Up Table.

MSB Most Significant Bit.

Mux Multiplexer.

NaN Not a Number.

PCI Peripheral Component Interconnect.

PCM Pulse Code Modulation.

PDM Pulse Density Modulation.

PL Programmable Logic.

**PS** Processing System.

PWM Pulse Width Modulation.

**RISC** Reduced Instruction Set Computer.

RMS Root Mean Square.

SA-CD Super Audio Compact Disc.

SB Switch Block.

SCL Serial Clock.

SDA Serial DAta.

**SoC** System on Chip.

**SRAM** Static Random Access Memory.

VHDL Very high speed integrated circuit HDL.

### 1 Introduction

L'une des innovations qui a permis la démocratisation globale de l'audionumérique est le convertisseur Sigma-Delta ( $\Sigma/\Delta$ ). Il propose une conversion très performante et peu coûteuse dès le début des années 1980. Vingt ans plus tard, Sony et Philips, avec la sortie du Super Audio Compact Disc, proposent de franchir le pas vers une chaîne du son entièrement  $\Sigma/\Delta$  au détriment de la modulation PCM. Cependant, le domaine de l'audio professionnel, en grande partie, ne suit pas, notamment par manque de solutions professionnelles accessibles. En effet, le traitement du son, vital pour la plupart des étapes d'une production sonore, se révèle être un défi technologique particulièrement complexe en  $\Sigma/\Delta$ .

Aujourd'hui, maintenant que la technologie du traitement numérique du signal a grandement évoluée. La question d'une chaîne du son cohérente entièrement en modulation  $\Sigma/\Delta$  peut à nouveau être posée. Nous devons alors commencer par vérifier si les traitements numériques du son, devenus essentiels aujourd'hui, sont réalisables pour une modulation  $\Sigma/\Delta$ . S'ils le sont, quels avantages et désavantages présentent ces traitements  $\Sigma/\Delta$  par rapport aux traitements numériques utilisés aujourd'hui. Ainsi pourrons-nous déterminer la place qu'occupera la modulation  $\Sigma/\Delta$  dans la chaîne audionumérique du futur.

Dans ce mémoire, nous allons étudier le traitement numérique de la dynamique d'un signal en modulation Sigma-Delta. L'une des raisons qui m'ont fait graviter autour de ce sujet est le paradoxe entre modulation 1 bit et évaluation du niveau. En effet, nous verrons dans quelles conditions nous pourrons évaluer le niveau d'un signal seulement composé de zéros et de uns.

Ce mémoire a pour volonté de s'inscrire dans la suite des mémoires de l'ENS Louis-Lumière traitants de la modulation  $\Sigma/\Delta$  [Payen de La Garanderie 2015, et Montpied 2019]. On souhaite ici introduire un nouveau type de traitement sonore pour la modulation  $\Sigma/\Delta$  et vérifier si ce modèle est viable pour une utilisation exigeante en matière de qualité sonore, comme la production musicale.

Dans la première partie, on définira les notions de modulation et modulateur  $\Sigma/\Delta$ . Mais avant, on exposera l'histoire des innovations technologiques qui ont fait évoluer la modulation  $\Sigma/\Delta$  et son utilisation.

Dans la partie suivante, on commencera par présenter la relation qui existe entre modulation  $\Sigma/\Delta$  et la dynamique d'un système numérique. Puis, après avoir expliqué le fonctionnement d'un compresseur de dynamique, on proposera un modèle numérique de compresseur de dynamique pour la modulation  $\Sigma/\Delta$ . Le modèle est éclaté en trois parties et chaque étape du traitement du signal est expliquée. Ainsi, les particularités du traitement de la modulation  $\Sigma/\Delta$  seront abordées.

Enfin, dans la troisième partie, nous réaliserons le modèle de compresseur proposé dans la partie précédente dans un système sur puce. Les outils logiciels et matériels utilisés seront présentés et l'on montrera comment réaliser une interface utilisateur pour ce compresseur. L'interface comprendra des potentiomètres pour contrôler les paramètres du compresseur ainsi qu'un indicateur de niveau.

# 2 Modulation Sigma-Delta

# 2.1 Historique & Utilisations

Depuis 1982, le signal audionumérique est principalement représenté sous la forme de modulation par impulsion et codage, appelée PCM (*Pulse Code Modulation*). Dans le domaine de l'audio grand public, la résolution et fréquence d'échantillonnage retenue est celle du CD-DA (*Compact Disc - Digital Audio*), à savoir 16 bits et 44,1 kHz, respectivement. Cependant, dans le domaine de l'audio professionnel on rencontre couramment une quantification de 24 bits pour une fréquence d'échantillonnage entre 44,1 et 192 kHz. Le traitement en temps réel de ce signal PCM se fait à l'aide de processeurs de traitement numérique du signal ou DSP (*Digital Signal Processor*). Dans le domaine de l'informatique, c'est le microprocesseur de l'ordinateur, associé au coprocesseur mathématique, qui réalise le traitement du son en PCM.

Au début de l'audionumérique, toute la chaîne audio était en modulation PCM de façon cohérente : la conversion analogique-numérique, le traitement audio et la conversion numérique-analogique.

La recherche de convertisseurs analogique-numérique et numériqueanalogique performants a conduit à l'utilisation de la modulation  $\Sigma/\Delta$ . Cette situation a engendré le recours à deux conversions supplémentaires  $\Sigma/\Delta$  vers PCM et PCM vers  $\Sigma/\Delta$ .

Dans ce travail, on cherche à rendre la chaîne audio cohérente en effectuant les deux opérations de conversion et de traitement en utilisant uniquement la modulation  $\Sigma/\Delta$ .

Dans cette partie, on va présenter le contexte historique pour comprendre comment la modulation  $\Sigma/\Delta$  se place dans cette chaîne audio et ce qu'elle propose comme alternatives et évolutions.

### 2.1.1 Conception de la Modulation Sigma-Delta

La modulation  $\Sigma/\Delta$  n'est pas une idée récente, elle fut théorisée dès 1952 et elle fut présentée comme une alternative plus performante et robuste que le PCM. Une illustration effectuée sous Matlab des apports de la modulation  $\Sigma/\Delta$  par rapport au PCM est donnée ci-dessous :

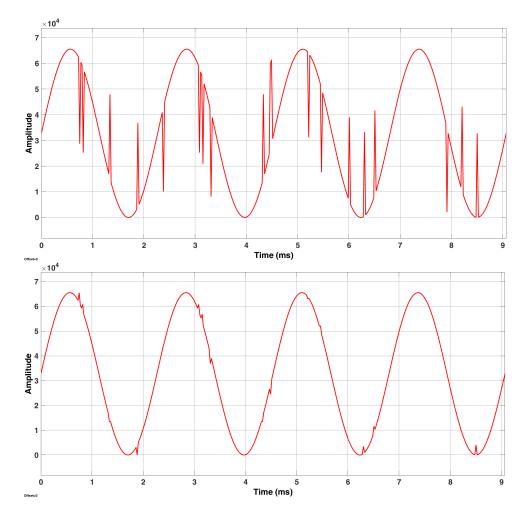

Figure 1 – Haut : Effet de la Modification du MSB (par Application de la Fonction Complément) de 5 % des Échantillons d'un Signal PCM (16 bits/44,1 kHz). Bas : Effet de la Modification des 12 bits de Poids les Plus Faibles de 5 % des Échantillons d'un Signal PCM (16 bits/44,1 kHz).

La figure 1 nous montre bien la vulnérabilité d'un signal PCM face à la corruption des bits de chacun de ses échantillons. La corruption du MSB des échantillons d'un signal PCM, l'affecte de manière considérable. En effet, le poids du MSB d'un échantillon représente la moitié de sa valeur totale.

Figure 2 – Effet de la Modification du Bit (par Application de la Fonction Complément) de 5 % des Échantillons d'un Signal  $\Sigma/\Delta$

La figure 2 montre qu'en modulation  $\Sigma/\Delta$ , la corruption d'un bit a moins d'effet sur l'intégrité du signal qu'en modulation PCM. En effet, en modulation  $\Sigma/\Delta$ , il y a un bit par échantillon et comme tous les bits ont des poids équivalents, la corruption d'un bit a moins d'effet sur l'intégrité de la forme d'onde finale.

L'une des premières applications concrètes de la modulation  $\Sigma/\Delta$  date de 1962 [Inose, Yasuda et Murakami 1962]. Avec celle-ci, la notion de mise en forme du bruit ainsi que le nom de modulation  $\Sigma/\Delta$  furent introduits. Cependant, avec 40 dB de dynamique et 5 kHz de bande passante le système aura besoin de plus de développement et ne paraît pas attractif à son époque. La raison étant que l'expansion des systèmes numériques n'est pas encore arrivée, donc la recherche ne s'intéresse pas encore à de meilleurs moyens de numériser un signal analogique.

Dans les années qui suivent, le convertisseur  $\Sigma/\Delta$  a fait l'objet de nouveaux travaux de recherche visant à améliorer ses performances. Ainsi, l'arrivée en 1982 du CD-DA, a nécessité le développement de convertisseurs performants, moins encombrants et à faible coût [Reefman et Janssen 2004]. Dès les années 1990, l'utilisation des convertisseurs  $\Sigma/\Delta$  s'est donc démocratisée. Les apports des convertisseurs  $\Sigma/\Delta$  par rapport aux convertisseurs PCM font que, la quasi-totalité des convertisseurs utilisés dans beaucoup de domaines, y compris en audiovisuel, sont basés sur les convertisseurs  $\Sigma/\Delta$ . Les convertisseurs PCM cèdent le terrain face aux convertisseurs  $\Sigma/\Delta$  de manière régulière.

#### 2.1.2 Super Audio Compact Disc

Figure 3 – Logos du Support SA-CD et du Format DSD

En 1998, un support entièrement 1 bit fût présenté : le Super Audio Compact Disc (SA-CD). La fréquence d'échantillonnage du SA-CD, appelée DSD64, est 64 fois plus élevée que celle du CD-DA; elle vaut 2,8224 MHz. Le SA-CD a été présenté par Philips et Sony comme le successeur du CD-DA et propose une nouvelle chaîne d'écoute où le  $\Sigma/\Delta$  n'est plus seulement une technologie interne des convertisseurs mais l'encodage de toute la chaîne du son. Le procédé de stockage de ce nouveau support est baptisé Direct Stream Digital (DSD).

En mars 1999, la première version du livret de spécification du SA-CD est éditée par Sony et Philips. Ce livret est nommé le "Scarlet Book", en sachant que le livret de spécification du CD-DA est nommé "Red Book", c'est encore une indication que le SA-CD était pensé comme une évolution du CD-DA.

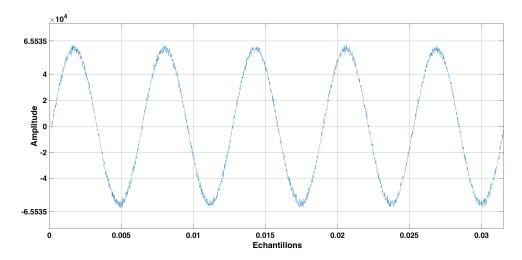

Il existe trois types de SA-CD: simple couche, double couche et hybride [Janssen et Reefman 2003]. Le type le plus courant est l'hybride; il associe une couche CD-DA conventionnelle, avec une couche DSD haute définition placée au-dessus de celle-ci. Cela rend le SA-CD hybride rétrocompatible avec les lecteurs CD-DA conventionnels. Les deux autres types de SA-CD ne comporte que des pistes DSD, sur une ou deux couches. La couche DSD d'un SA-CD contient une piste multicanal 5.1 ainsi qu'une piste stéréo séparée.

En sachant qu'une couche DSD d'un SA-CD peut stocker 4,7 Go de données, voici le calcul de la durée en minutes d'un programme audio  $\Sigma/\Delta$  à 1 bit en stéréo et en 5.1 avec une fréquence d'échantillonnage de 64 fois 44,1 kHz :

Figure 4 – Agencement des Couches d'un SA-CD Hybride [Janssen et Reefman 2003, Figure 1, p.1]

$$t_{pgm} = \frac{8 \cdot 4, 7 \cdot 10^9}{1 \cdot 64 \cdot 44\,100 \cdot (6+2) \cdot 60} \approx 27\,min\,45\,sec$$

Cependant, chaque couche DSD d'un SA-CD propose 74 minutes de programme. Pour pouvoir stocker un programme de cette longueur, le débit doit être réduit sans perte (couramment appelé compression de donnée), avec un ratio d'environ 2,7. Ce procédé est appelé DST pour *Direct Stream Transfert*. L'encodage DST repose sur un filtre à prédiction linéaire et du codage entropique que nous ne présenterons pas ici [Janssen, Knapen et al. 2004]. Les procédés de compression sans pertes qui existent pour les formats PCM ne peuvent pas être utilisés efficacement sur un signal 1 bit. Souvent, la modulation  $\Sigma/\Delta$  est appelée DSD par abus de langage, même si elle ne comporte de pas de compression DST.

### 2.1.3 Solutions de Traitement DSD en Temps-Réel

Le traitement en temps réel du flux DSD reste un problème difficile à régler. En effet, même si c'est théoriquement possible, la plupart des DSP ne sont pas assez performants pour cette application. Nous allons approfondir deux innovations qui contournent le problème de manière similaire : le procédé DSD-Wide de Sony [P. Thorpe et al. 2001] et le procédé Digital eXtreme Definition (*DXD*) de Merging Technologies [Vest 2004].

Ces deux solutions ont été développées avec le souci du maintien de l'ergonomie de travail des professionnels du son en tête. Elles font le constat que la production d'un SA-CD nécessite un environnement de travail qui permet d'éditer et de traiter des flux DSD de façon simple et sans faire de compromis sur la qualité originale du flux DSD.

#### 2.1.3.1 DSD-Wide

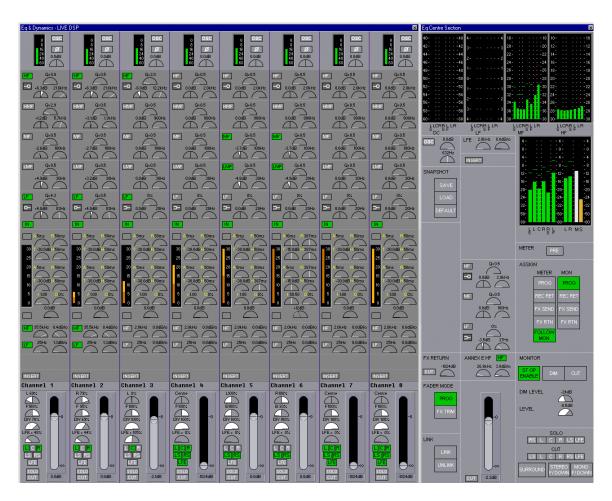

Figure 5 – L'Interface Utilisateur de la Console de Mastering Proposée par la Carte DSD-Wide [P. Thorpe et al. 2001, Figure 15, p.12]

Sony propose en 2001 le DSD-Wide qui est une matérielle (hardware). C'est une carte d'extension de type PCI (Peripheral Component Interconnect) équipée de sept puces de réseaux logiques programmables de type FPGA (Field Programmable Gate Array). Le format audionumérique utilisé à l'intérieur de la carte est de résolution 8 bits, avec la même fréquence d'échantillonnage que le DSD, soit  $64 \times 44, 1kHz = 2,8224MHz$ . La caractéristique importante du format DSD-Wide est qu'il est parfaitement com-

patible avec le DSD. C'est-à-dire que la conversion, dans les deux sens, n'entraîne pas de perte de qualité.

Au final, comme dans la figure 5, la carte DSD-Wide peut proposer une console de mastering en 5.1 et en stéréo avec un jeu complet de traitements numériques : Niveau, Panoramique, Égalisation et Dynamique.

### 2.1.3.2 Digital Extreme Definition

Figure 6 – Le Logo du Format DXD [Merging Technologies ρ. d.(b)]

La solution de Merging Technologies intègre des éléments logiciels (software) et matériels (hardware). L'idée principale est de permettre aux utilisateurs de leur DAW Pyramix de produire un SA-CD en qualité DSD de l'enregistrement au mastering.

Pour ce faire, Merging Technologies a proposé un format propriétaire appelé DXD pour "Digital eXtreme Definition". Le DXD est un format PCM 24 bits avec une fréquence d'échantillonnage de 352,8 kHz (8 fois 44,1 kHz). Comme le format interne du DSD-Wide, le but est de pouvoir convertir le DXD en DSD sans perte de qualité. Ainsi, le DXD est édité et traité de la même manière qu'un signal PCM ordinaire. L'ambiguïté de la dynamique du signal est levée, ce qui rend le contrôle du niveau au VU-mètre aisé.

Un des avantages de cette conversion PCM est qu'il suffit qu'un plugin de traitement puisse accepter le format suréchantillonné du DXD pour pouvoir le traiter. Ainsi, Merging Technologies fournit une liste des plug-ins compatibles DXD [Merging Technologies p. d.(a)].

#### 2.1.4 Évolution du FPGA

Les réseaux logiques programmables de type FPGA (*Field Programmable Gate Array*) ont étés introduits par l'entreprise américaine Xilinx en 1985. En résumé, un FPGA est une puce qui peut être programmée pour créer

n'importe quel circuit logique en son sein.

Au moment de la création du FPGA, les fonctions logiques étaient réalisées au moyen de circuits logiques discrets. La réalisation d'une nouvelle fonction nécessite la conception d'un nouveau circuit. Le FPGA a été développé comme solution à ce problème. Ainsi, si une modification de la fonction du circuit est à faire il suffit de reprogrammer le FPGA [Woods et al. 2017]. Dans le travail d'ingénieur électronique, cela permet de dissocier le travail de fabrication du circuit imprimé de celui de conception du circuit logique.

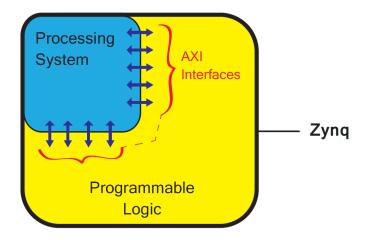

À ses débuts, le FPGA est donc vu comme un composant "glue" qui relie tous les composants d'un système pour le rendre plus complexe et configurable. Le succès du FPGA lui a permis de beaucoup évoluer depuis sa création. Il a commencé à être vu comme une solution complète pour une variété de problèmes. En effet, avec les avancées technologiques des semiconducteurs, le nombre de transistors par unité de surface (densité) dans une puce à grandement augmenté (loi de Moore). Á l'aube des années 2000, on à commencé à associer les FPGA aux microprocesseurs dans une même puce. De nos jours, ces plateformes hétérogènes sont appelées systèmes sur puces ou SoC (System on Chip).

Les FPGA ont un attrait particulier dans le domaine du traitement numérique du signal pour plusieurs raisons. En premier lieu, les FPGA modernes possèdent une grande puissance de calcul. De plus, contrairement aux processeurs, un FPGA peut effectuer un grand nombre de traitements en même temps [Eastty, Sleight et P. D. Thorpe 1997]. En effet, le FPGA est un circuit logique et non pas un processeur qui doit suivre un algorithme de manière linéaire. Un FPGA peut donc avoir différentes horloges non synchrones et faire des opérations complexes exactement en même temps.

Le recours à un FPGA dans un équipement audionumérique est justifié par le fait qu'il constitue une alternative intéressante vis-à-vis des DSP. Ainsi, le FPGA permettrait de réaliser une chaîne audio cohérente travaillant en modulation S/D allant de la captation à la diffusion.

### 2.2 Modulation Sigma-Delta

Tout d'abord, une mise au point du vocabulaire s'impose : le flux de sortie d'un modulateur  $\Sigma/\Delta$ , désigné  $\Sigma/\Delta$ -M (Sigma-Delta Modulator), est appelé par abus de langage modulation  $\Sigma/\Delta$ . Cependant, il est aussi possible de rencontrer l'appellation modulation de densité d'impulsion (PDM pour Pulse Density Modulation). Cette PDM est équivalente, à fréquence d'échantillonnage constante, à la modulation de largeur d'impulsion (PWM pour Pulse Width Modulation).

Ainsi, dans le jargon technique,  $\Sigma/\Delta$ , PDM, DSD et même PWM sont souvent utilisés de façon interchangeable.

Contrairement à la modulation par impulsion et codage, la forme d'onde de la modulation  $\Sigma/\Delta$  ne ressemble pas à celle d'un signal analogique de prime abord. En effet, on peut se figurer l'amplitude de la forme d'onde originale seulement avec le rapport cyclique (duty cycle) de la modulation  $\Sigma/\Delta$ . Comme suggéré par le nom "modulation à densité d'impulsion", lorsque le signal  $\Sigma/\Delta$  est souvent au maximum c'est que l'amplitude doit être proche du maximum, de même pour le minimum. Lorsqu'il y a l'air d'avoir autant de 0 que de 1, c'est que l'amplitude est proche de 0.

Figure 7 – Encodage d'un signal sinusoïdal en  $\Sigma/\Delta$  1 bit [Ogier 2021]

Appelé aussi convertisseur à suréchantillonnage, un convertisseur  $\Sigma/\Delta$  utilise une fréquence d'échantillonnage  $f_s$  égale à celle d'un convertisseur PCM multipliée par un certain facteur  $N_0$ . Typiquement, ce facteur est 64, ce qui donne une fréquence d'échantillonnage de  $N_0 \cdot f_s = 64 \times 44, 1kHz = 2,8224MHz$ . On rencontre aussi des facteurs de suréchantillonnage de 128 et 256.

La fréquence de Nyquist se retrouve donc dans la bande des ultrasons. Cependant, un repli spectral est toujours possible. Un filtrage des fréquences supérieures à la fréquence de Nyquist est donc toujours nécessaire, mais facilité par la fréquence d'échantillonnage qui est très haute par rapport à la bande audio à préserver.

La sortie du  $\Sigma/\Delta$ -M est déterminée par l'erreur de conversion accumulée.c'està-dire que l'écart entre la valeur analogique et la valeur numérique. Cet écart représente l'erreur de quantification calculée à chaque échantillon. Puis, elle est accumulée, on l'additionne aux erreurs de quantification précédentes. Si cette accumulation est positive, l'échantillon sera un 1. Il sera un 0 si l'accumulateur a une valeur négative. Ainsi, par nature, la valeur d'un échantillon dans un flux  $\Sigma/\Delta$  dépend de la valeur des échantillons précédents. Cette caractéristique est autre une particularité d'un convertisseur  $\Sigma/\Delta$  qui est absente dans un convertisseur PCM qui quantifie les échantillons individuellement.

# 2.3 Modulateur Sigma-Delta

Pour qu'un système numérique puisse traiter un signal audio, nous devons transformer ce signal en une suite d'échantillons quantifiés. En audio, ces échantillons sont prélevés à une fréquence constante  $F_s$ . Le rôle du modulateur est donc de convertir le signal d'entrée en une modulation numérique spécifique, en vue d'être interprétée par un système numérique.

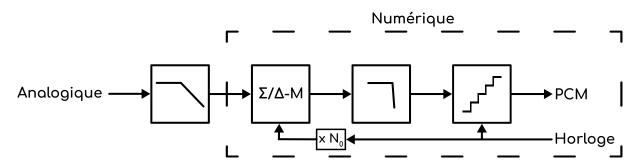

Un convertisseur analogique-numérique ou ADC (*Analog to Digital Converter*) à suréchantillonnage moderne opère selon le principe décrit par le schéma de la figure 8.

On fait passer le signal d'entrée par un filtre analogique d'ordre faible afin de ne convertir aucune fréquence supérieure à la fréquence de Nyquist du modulateur  $\Sigma/\Delta$ . On peut se permettre d'utiliser un filtre de faible ordre, car la fréquence d'échantillonnage du  $\Sigma/\Delta$ -M est un multiple de la fréquence

d'échantillonnage cible, la fréquence de Nyquist est donc bien plus élevée. Ensuite, le flux  $\Sigma/\Delta$  est passé à travers un filtre numérique avec un ordre élevé, son rôle est de filtrer les fréquences supérieures à la fréquence de Nyquist de la fréquence d'échantillonnage cible.

Enfin, la sortie du filtre est quantifiée sur le nombre de bits souhaité, à la fréquence d'échantillonnage cible. On retrouve alors une modulation PCM en sortie.

Employer un  $\Sigma/\Delta$ -M pour déporter le filtrage anti-repliement d'ordre élevé dans le domaine numérique est une technique qui a permis d'une part d'améliorer la qualité des convertisseurs et d'autre part de réduire leurs coûts de fabrication.

Figure 8 – Schéma Fonctionnel d'un ADC à Suréchantillonnage avec une Sortie PCM

Maintenant, nous allons nous intéresser seulement au modulateur  $\Sigma/\Delta$ , car il est l'élément principal de l'ADC si on souhaite un flux  $\Sigma/\Delta$  en sortie.

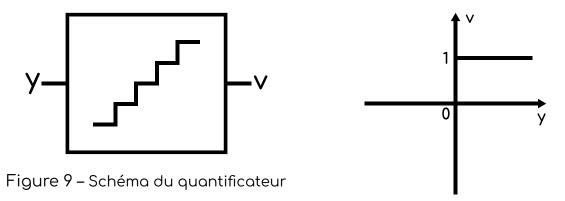

Comme son analogue PCM, le modulateur  $\Sigma/\Delta$  ( $\Sigma/\Delta$ -M) est basé autour d'un quantificateur. Le quantificateur est un système non linéaire qui est défini par ses caractéristiques statiques d'entrée/sortie [Schreier et Temes 2005]. L'entrée d'un quantificateur est généralement appelée Y et la sortie V.

En d'autres termes, c'est l'élément qui est chargé de transformer un signal en une suite d'échantillons d'une valeur quantifiée en un nombre de bits quelconque. L'audio en 1 bit sous-entend un quantificateur 1 bit avec des caractéristiques similaires à la Figure 10.

Figure 10 – Caractéristiques y/v d'un quantificateur bipolaire 1 bit

Un modulateur PCM est constitué uniquement d'un quantificateur. Dans le cas d'un  $\Sigma/\Delta$ -M, nous devons ajouter les parties qui lui confèrent son nom. Pour toutes les explications suivantes, nous allons nous limiter à un  $\Sigma/\Delta$ -M 1 bit du premier ordre.

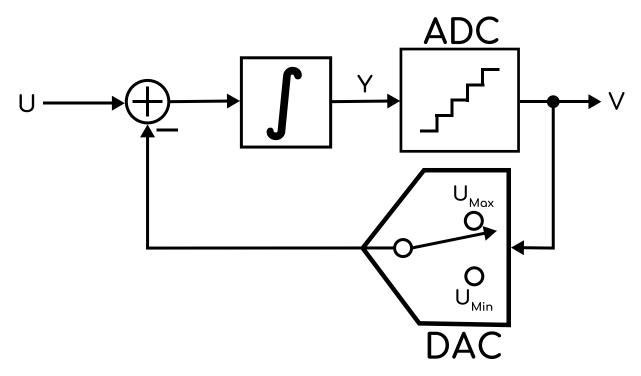

Lorsqu'un modulateur  $\Sigma/\Delta$  est utilisé dans un ADC, il est composé d'un quantificateur 1 bit, d'un filtre intégrateur et d'un convertisseur numérique-analogique 1 bit ou DAC (*Digital to Analog Converter*). Le DAC 1 bit consiste seulement à un multiplexeur qui commute entre la valeur maximale et minimale de l'entrée U.

Figure 11 – Schéma d'un Σ/Δ-M utilisé comme ADC [d'après Schreier et Temes 2005, Figure 2.12 a, p.30]

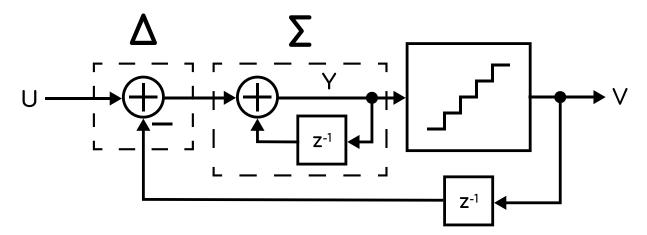

On simplifie le schéma en supposant que  $U_{Max} = VMax$  et en passant dans le domaine z. En domaine z, le filtre intégrateur peut être remplacé par un simple accumulateur. Le schéma du  $\Sigma/\Delta$ -M devient :

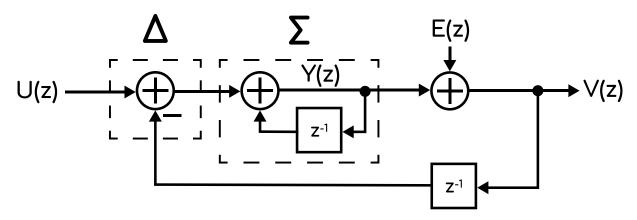

Figure 12 – Schéma d'un Σ/Δ-M 1 bit de premier ordre dans le domaine z [d'après Schreier et Temes 2005, Figure 2.16, p.33]

La figure 12 nous montre le système qui s'articule autour du quantificateur. La partie  $\Delta$  est la soustraction de l'entrée par la sortie de l'échantillon précédent. Cette opération donne l'erreur de quantification.

Quand on parle de l'ordre du  $\Sigma/\Delta$ -M, on parle de l'ordre du filtre de sa partie  $\Sigma$ . Dans notre cas, c'est un filtre de premier ordre, mais un convertisseur du marché utiliserait un filtre du cinquième ou sixième ordre. Le quantificateur a ici les caractéristiques de la Figure 10. Il a donc 0 en sortie quand l'erreur accumulée est négative et 1 quand elle est positive.

# 3 Traitement Dynamique en Sigma-Delta

# 3.1 Dynamique en Sigma-Delta

#### 3.1.1 Mise en Forme du Bruit

D'après le théorème de quantification de Widrow [Widrow 1961], un quantificateur peut-être modélisé de manière linéaire par la somme d'un bruit blanc au signal d'entrée. Cette approximation est valide dans le cas où l'amplitude du signal d'entrée est grande et que le bruit n'est pas corrélé avec ce dernier. Dans ces conditions, on peut considérer la quantification comme un ajout aléatoire de bruit, appelé bruit de quantification. Le bruit de quantification est noté E(z) dans la Figure 13 et dans les calculs suivants. Nous allons pouvoir analyser le niveau du bruit de fond d'un  $\Sigma/\Delta$ -M du premier ordre.

Figure 13 – Modèle linéaire d'un Σ/Δ-M de premier ordre dans le domaine z [d'après Schreier et Temes 2005, Figure 2.18, p.36]

D'après la Figure 13 on a :

$$Y(z) = U(z) - z^{-1}V(z) + z^{-1}Y(z)$$

Or:

$$\begin{split} V(z) &= Y(z) + E(z) \\ &= U(z) - z^{-1}V(z) + z^{-1}Y(z) + E(z) \\ &= U(z) + E(z) - z^{-1} \big(V(z) - Y(z)\big) \\ &= U(z) + E(z) - z^{-1}E(z) \\ &= U(z) + (1 - z^{-1})E(z) \end{split}$$

On remarque que la sortie d'un  $\Sigma/\Delta$ -M linéarisé n'est d'autres que son

entrée et le bruit de quantification filtré. En effet,  $(1-z^{-1})E(z)$  représente le bruit filtré par un filtre coupe-bas du premier ordre. Pour mettre cela en évidence, voici le calcul de la fonction de transfert du filtre appliqué au bruit.

$$H_{bruit}(z) = 1 - z^{-1}$$

Pour avoir  $H_{bruit}(f)$  il suffit de substituer z à  $e^{j\cdot \frac{2\cdot \pi\cdot f}{N_0\cdot Fs}}$ . Avec j le nombre complexe tel que  $j^2=-1$ ,  $N_0$  le facteur de suréchantillonnage et  $F_s$  la fréquence d'échantillonnage de base.

$$H_{bruit}(f) = 1 - e^{-j \cdot \frac{2 \cdot \pi \cdot f}{N_0 \cdot Fs}}$$

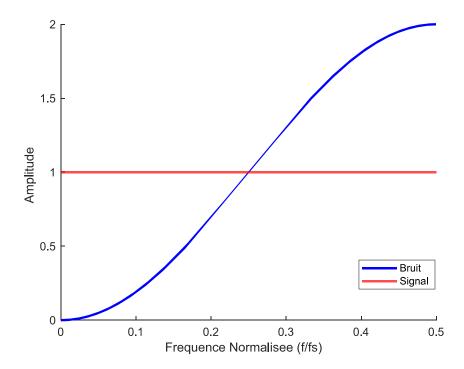

Figure 14 – Fonctions de transfert du signal et du bruit de quantification dans un  $\Sigma/\Delta$ -M du premier ordre

Une des grandes caractéristiques du  $\Sigma/\Delta$ -M est mise en évidence ici, le bruit de fond n'est pas de niveau uniforme sur tout le spectre. Cette caractéristique est appelée mise en forme du bruit ou "Noise-Shaping", le bruit est donc concentré dans la partie haute du spectre. Par conséquent, la dynamique du  $\Sigma/\Delta$ -M dépend de la fréquence. Ceci n'est pas le cas en

PCM.

De plus, cela met en avant l'importance de l'ordre du filtre présent dans le  $\Sigma/\Delta$ -M, plus l'ordre est élevé plus le Noise-Shaping est intense. De cette manière, on réduit le niveau du bruit présent dans la plage fréquentielle utile au signal.

#### 3.1.2 Calcul de Dynamique

On définira la dynamique d'un système numérique par le rapport signal sur bruit exprimé en décibels. Le calcul de la dynamique est donc :

$$Dyn = 10 \cdot \log_{10} \left( \frac{P_{EffMax}}{P_{Bruit}^{f_0}} \right)$$

Avec  $P_{EffMax}$  étant la puissance efficace d'un signal d'entrée au maximum de l'amplitude permise par le modulateur.  $P_{Bruit}$ , est la puissance du bruit de fond.

Avec un signal d'entrée sinusoïdal d'amplitude  $V_{Max}$ , l'expression de la dynamique devient :

$$Dyn = 10 \cdot \log_{10} \left( \frac{V_{Max}^2}{2} \right)$$

$$= 20 \cdot \log_{10} \left( \frac{V_{Max}}{\sqrt{2}} \right) - 10 \cdot \log_{10} (P_{Bruit}^{f_0})$$

Dans le modèle linéaire de la figure 13, la seule source de bruit est le bruit de quantification, nous allons donc calculer sa puissance.

Prenons un quantificateur qui sature au-delà de l'intervalle  $[-V_{Max},V_{Max}]$ . Au sein de cet intervalle, le modulateur a un pas de discrétisation de valeur  $\Delta$ . Dans le cas d'un  $\Sigma/\Delta$ -M 1 bit, le quantificateur a les caractéristiques de la figure 10. On a donc :

$$\Delta = V_{Max}$$

Le bruit d'un quantificateur vient de la différence d'amplitude entre le

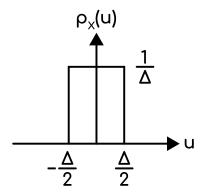

signal continu d'entrée et le signal échantillonné de sortie. L'intervalle d'erreur possible est donc :  $\left[-\frac{\Delta}{2},\frac{\Delta}{2}\right]$ . Si l'on suppose cette erreur aléatoire, on peut exprimer la densité de probabilité d'erreur suivante :

$$p_X(u) = \frac{1}{\Delta} \cdot \prod \left(\frac{u}{\Delta}\right)$$

Figure 15 – Densité de Probabilité de l'Erreur de Quantification

Avec u l'erreur de quantification et  $\prod \left(\frac{u}{\Delta}\right)$  la fonction rectangle centrée en 0 et de largeur  $\Delta$ .

La puissance du bruit de fond  $\sigma_X^2$  est calculée grâce à la variance de la densité de probabilité  $p_X(u)$ . Le calcul de la variance d'une variable aléatoire X est :

$$Var(X) = \mathbb{E}[X^2] - (\mathbb{E}[X])^2 = \sigma_X^2$$

Avec  $\mathbb{E}[X^k]$  le moment d'ordre k de la variable aléatoire X dont le calcul est :

$$\mathbb{E}[X^k] = \int_{-\infty}^{\infty} u^k \cdot p_X(u) \, du$$

Dans le cas d'une variable aléatoire distribuée uniformément les deux premiers ordres de moments sont donnés par [Zölzer 2008] :

$$\mathbb{E}[X] = \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} u \cdot p_X(u) \, du$$

$$= \frac{1}{\Delta} \cdot \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} u \, du$$

$$= 0$$

$$\mathbb{E}[X^2] = \int_{-\infty}^{\infty} u^2 \cdot p_X(u) \, du$$

$$= \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} \frac{u^2}{\Delta} \, du$$

$$= \frac{\Delta^2}{12}$$

Donc:

$$Var(X) = \mathbb{E}[X^2] = \sigma_X^2 = \frac{\Delta^2}{12}$$

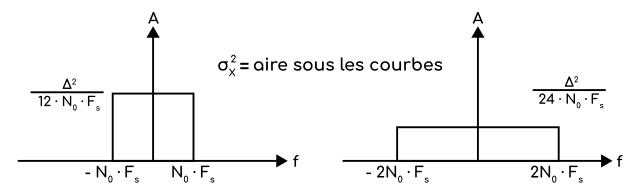

La puissance du bruit de quantification  $\sigma_X^2$  est répartie sur toute la période spectrale  $[-N_0\cdot F_s,N_0\cdot F_s]$ . Avec  $N_0$  le facteur de suréchantillonnage, et  $F_s$  la fréquence d'échantillonnage de base. C'est l'un des avantages du suréchantillonnage, le niveau du bruit de quantification est plus bas car la puissance du bruit est répartie sur un intervalle plus grand.

Le calcul de la répartition spectrale du bruit de quantification  $P_{BB}(f)$  est donc :

$$P_{BB}(f) = \frac{\sigma_X^2}{N_0 \cdot F_s}$$

$$= \frac{\Delta^2}{12 \cdot N_0 \cdot F_s}$$

Figure 16 – Niveau du Bruit de Quantification en Fonction du Facteur de Sur-Échantillonnage [d'après Laroche 1995, p.10]

Il faut maintenant prendre en compte la caractéristique de mise en forme du bruit, propre au  $\Sigma/\Delta$ -M. Pour cela il suffit de multiplier la répartition spectrale du bruit par le module au carré de la fonction de transfert du bruit  $H_{bruit}(f)$ . Cela nous donne la densité spectrale du bruit  $D_{Bruit}(f)$ .

$$P_{Bruit}(f) = P_{BB}(f) \cdot |H_{bruit}(f)|^2$$

$$= \frac{\Delta^2}{12 \cdot N_0 \cdot F_s} \cdot |H_{bruit}(f)|^2$$

Intégrer la densité spectrale du bruit sur  $[-f_0,f_0]$  permet de récupérer la puissance du bruit de fond dans la bande  $[0,f_0]$ . Avec  $f_0=0,5\cdot F_s$  on pourra calculer la puissance du bruit de fond dans la bande de fréquences utile. C'est cette puissance qui intervient dans le calcul de la dynamique.

$$P_{Bruit}^{f_0} = \int_{-f_0}^{f_0} P_{Bruit}(f) df$$

$$= \int_{-f_0}^{f_0} P_{BB}(f) \cdot |H_{bruit}(f)|^2 df$$

$$= \frac{\Delta^2}{12 \cdot N_0 \cdot F_s} \cdot \int_{-f_0}^{f_0} |H_{bruit}(f)|^2 df$$

Le détail des calculs peuvent être trouvé dans [Payen de La Garanderie 2015, p23-25]. On obtient :

$$|H_{bruit}(f)|^2 = \left(\frac{2 \cdot \pi \cdot f}{N_0 \cdot F_s}\right)^2$$

$$P_{Bruit}^{f_0} = \frac{\Delta^2}{12} \cdot \frac{\pi^2}{3} \cdot \left(\frac{2 \cdot f_0}{N_0 \cdot F_s}\right)^3$$

$$Dyn = 6,02 \cdot \left(N_b - 1 + 1, 5 \cdot (r - 1)\right) + 2,61 - 30 \cdot \log_{10}\left(\frac{f_0}{F_s}\right)$$

Avec r un facteur de suréchantillonnage tel que  $N_0=2^r$  et  $N_b$  le nombre de bits du signal de sortie du modulateur tel que  $\Delta=\frac{2\cdot V_{Max}}{2^{N_b}-1}$ .

Faisons l'application numérique avec les paramètres suivants :

- Quantification de 1 bit,  $N_b = 1 bit$ .

- Facteur de suréchantillonnage de 64,  $r = log_2(64) = 6$ .

- Fréquence d'échantillonnage de base de 44,1 kHz,  $F_s=44\,100\,Hz$ .

- Une bande passante de  $\left[0, \frac{F_s}{2}\right]$ ,  $f_0 = 22\,050\,Hz$ .

On trouve:

$$Dyn \approx 56, 8 dB$$

C'est un résultat bien inférieur à la dynamique du CD-DA qui est aux alentours de 96 dB. Il y a plusieurs solutions pour pallier à ce problème :

- Augmenter le facteur de suréchantillonnage. En effet, doubler le facteur de suréchantillonnage  $N_0$  (ajouter 1 à r) augmente la dynamique d'environ 9 dB.

- On pourrait faire une quantification sur plus de bits. Chaque bit supplémentaire représente environ 6 dB de dynamique supplémentaire. C'est la solution qu'adopte certains ADC en incorporant des étages multi bits dans leur Σ/Δ-M d'ordre élevé. Par souci de simplicité, ce n'est pas une solution que nous explorerons dans ce mémoire.

- Augmenter l'ordre du modulateur. Avoir un filtre d'ordre supérieur permettrait d'accentuer la propriété de mise en forme du bruit du

Σ/Δ-M. Ainsi, la densité spectrale du bruit de quantification est encore plus concentrée dans les hautes fréquences et dégage le bruit de la bande passante.

Autant de raisons pour lesquelles la plupart des puces de convertisseurs comportent des modulateurs d'ordre 4, 5 ou supérieurs. De plus, il est commun de voir des facteurs de sur échantillonnage de 128 ou 256. Cependant, étudier le cas d'un  $\Sigma/\Delta$ -M de premier ordre est plus simple.

# 3.2 Fonctionnement d'un Compresseur Dynamique

#### 3.2.1 Fonction

Un compresseur est un outil de traitement du signal audio qui permet de réduire la plage dynamique d'un son. Le compresseur réalise cette tâche en réduisant le niveau sonore lors des moments où le signal d'entrée est le plus fort.

Ses réglages peuvent lui permettent d'intervenir sur la micro dynamique ou la macro-dynamique du son. C'est-à-dire des temps très courts comme un coup de caisse claire ou des temps assez longs comme les différents mouvements d'une symphonie.

Aujourd'hui le compresseur est un élément essentiel de beaucoup de productions sonores. En production musicale, beaucoup de sonorités modernes sont définies en grande partie par le rôle adopté par le compresseur. Ainsi, la diversité des modèles de compresseurs est à l'image de la grande diversité d'applications qui lui sont attribuées.

C'est pour cela qu'il n'est pas aisé de résumer la totalité des fonctionnalités qui ont été ajoutées au compresseur. Cependant, nous allons nous concentrer sur les fonctions principales et celles qui seront implémentées dans notre compresseur  $\Sigma/\Delta$ .

#### 3.2.2 Seuil & Rotio

Le seuil de compression (threshold en anglais) peut être considéré comme le paramètre principal d'un compresseur dynamique. Le seuil de compression indique le niveau à partir duquel la compression est enclenchée. Quand le niveau du signal appliqué à l'entrée du compresseur dépasse ce

seuil, le niveau sonore est baissé de manière proportionnelle à un ratio.

Ce ratio est souvent exprimé en fonction de combien de décibels en entrée, une fois passé le seuil, sont nécessaires pour augmenter le niveau de sortie de 1 dB. On peut donc associer le ratio à l'agressivité de la compression.

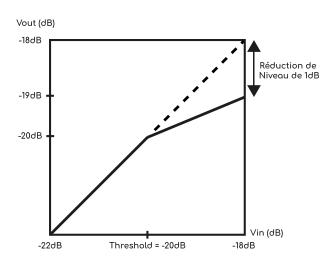

Par exemple, pour un ratio de 2 : 1, un seuil de -20 dB et un niveau continu à -18 dB en entrée, le compresseur réduira le niveau sonore du signal traité de 1 dB (Figure 17). Si le ratio est était de 4 : 1, la réduction serait de 1,5 dB. Si le ratio est infini, le compresseur devient un limiteur, la réduction du gain devient alors égale au niveau dépassant le seuil.

Vout (dB)

-20dB

-20dB

-20dB

Threshold = -20dB

-18dB

Figure 17 – Réponse dynamique d'un compresseur avec un ratio de 2 : 1 et un seuil de -20 dB

Figure 18 – Comparaison des réponses dynamiques d'un compresseur Hard Knee et Soft-Knee

On peut faire en sorte d'avoir un ratio qui évolue en fonction du niveau d'entrée du compresseur. Cette caractéristique s'appelle le *knee*. Ce nom fait référence à la jointure de la réponse dynamique au niveau du seuil. Dans la figure 18, on voit deux façons de traiter la transition de la compression au niveau du seuil.

Le "hard knee" compresse le signal, avec le ratio maximum, dès que le niveau détecté a dépassé le seuil. Le "soft knee" quant à lui fait une transition "douce" et augmente le ratio de compression un peu avant le seuil et n'est pas encore au ratio indiqué directement après le seuil. Certains compresseurs permettent de régler la largeur du knee.

#### 3.2.3 Détection

La façon dont le niveau d'entrée du compresseur est évalué influe sur la totalité du comportement d'un compresseur. Le circuit de détection initie un signal de niveau détecté (appelé *sidechain* en anglais). Le niveau détecté peut être évalué de façons différentes.

On distingue ici les compresseurs dits "peak" et "RMS" (Root Mean Square ou valeur efficace).

Les compresseurs *peak* détectent le niveau absolu des crêtes du signal. Ils sont plus facilement réalisables en numérique et peuvent servir à effectuer des corrections très rapides.

Une détection RMS est facilement intégrée dans un compresseur analogique, ici on détecte la valeur efficace du signal. On agit donc plus facilement sur la macro-dynamique.

Certains compresseurs permettent de choisir où est prélevé le signal du détecteur. Si le signal de sidechain est prélevé avant le circuit de réduction de niveau, le compresseur est de type "feed-forward". Si le sidechain détecte le niveau après le circuit de réduction de niveau le compresseur de type "feedback". Les compresseurs feed-forward sont privilégiés pour un traitement précis et rapide du son, un modèle classique de compresseur feed-forward étant l'Urei 1176LN. Les compresseurs feedback, quant à eux, sont privilégiés pour un traitement doux et lent du signal, un modèle classique de compresseur feedback étant le Teletronix LA-2A.

De plus, des options avancées d'un compresseur peuvent inclure un filtrage du signal avant la détection de niveau. C'est une option qui permet de sculpter la réponse du compresseur en fonction du contenu fréquentiel du signal d'entrée. Par exemple, couper les basses du signal de sidechain voudra dire que le compresseur réagira moins fortement aux composantes graves du signal sonore.

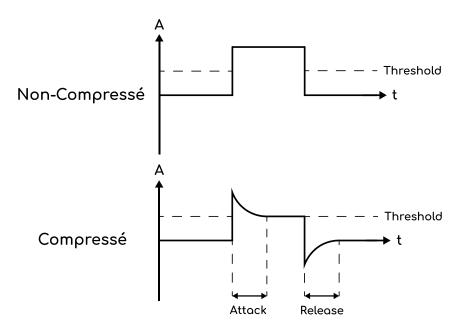

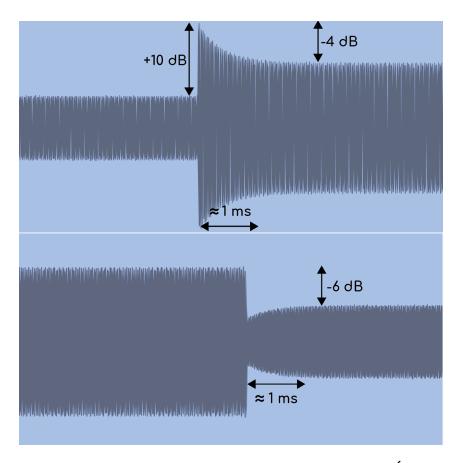

#### 3.2.4 Réponse Temporelle

La rapidité de réaction du compresseur peut être réglée. Ainsi, le temps d'attaque (attack) détermine le temps que mettra le compresseur à s'activer et le temps de retour (release) détermine le temps que met le compresseur à revenir à son état initial. Par exemple, si le niveau du détecteur dépasse le seuil pendant un temps plus court que le temps d'attaque, le

compresseur ne réagira pas.

Figure 19 – Effet d'un Compresseur sur un Signal Rectangulaire

La figure 19 met en évidence le temps d'attaque et de retour pour un compresseur avec un ratio infini. On remarquera que dans ce cas, les temps d'attaque et de retour sont similaires.

Les compresseurs numériques ont introduit une façon de pouvoir détecter le signal en avance appelée le "look-forward". Il s'agit juste d'introduire du délai au signal par rapport au sidechain, mais cela permet de décaler à volonté le signal de réduction de gain par rapport à l'audio.

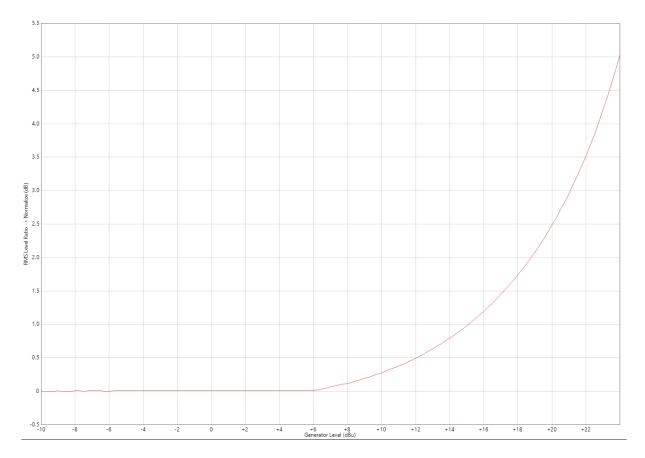

#### 3.2.5 Signal de Sortie

Comme un compresseur peut réduire considérablement le niveau du signal traité, il est essentiel de pouvoir augmenter le niveau de sortie afin de compenser la réduction de niveau sonore perçu. En effet, le but principal d'un compresseur est seulement de réduire la plage dynamique du signal traité, pas forcément de réduire son niveau sonore général. Cette compensation de gain est souvent appelée *makeup gain*.

Certains compresseurs proposent en sortie un mixeur entre le signal d'entrée et le signal de sortie du compresseur. Mélanger ces deux signaux s'appelle de la compression parallèle.

#### 3.2.6 Couplage

Quand un compresseur traite un signal stéréo, il est souvent utile de coupler les compressions de chaque canal entre elles (stereo linking). C'est-à-dire que, par exemple, pour les mêmes réglages de détection, si seulement le canal gauche dépasse le seuil et déclenche la compression, le canal droit est compressé de la même façon. C'est une façon de procéder pour avoir une image stéréo plus stable. Il est aussi possible d'utiliser une seule chaîne de détection pour la somme des deux canaux, mais cette technique supprime l'option de découpler les paramètres des deux canaux.

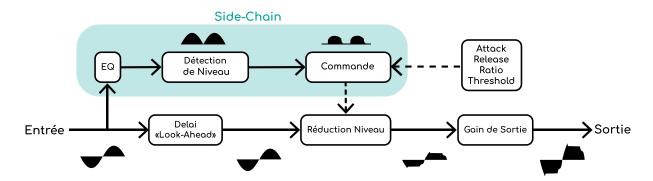

Figure 20 – Schéma Fonctionnel d'un compresseur *Feed-Forward* avec Equalisation de *Side-Chain* et "Look-Ahead"

# 3.3 Conception du Compresseur Dynamique Sigma-Delta

Réaliser un compresseur  $\Sigma/\Delta$  pourrait présenter des caractéristiques intéressantes par rapport à un compresseur PCM. La fréquence d'échantillonnage est bien supérieure, ce qui permet d'avoir un temps de réduction de gain extrêmement rapide. Cela peut être une caractéristique recherchée pour un limiteur.

De plus, la latence introduite par le traitement numérique d'un signal  $\Sigma/\Delta$  est souvent très faible. Ce qui peut aussi être une caractéristique recherchée dans les applications où la rapidité d'exécution est essentielle.

Le modèle de compresseur que nous souhaitons réaliser est un compresseur capable d'exploiter les capacités d'un compresseur numérique et du format DSD c'est-à-dire un modèle proche de celui de la Figure 20, notamment une détection de crête très efficace grâce à l'architecture feedforward.

C'est pour cette raison que la fréquence d'échantillonnage n'est pas réduite dans le *sidechain*. Ainsi, chaque échantillon DSD est associé à un gain de compression.

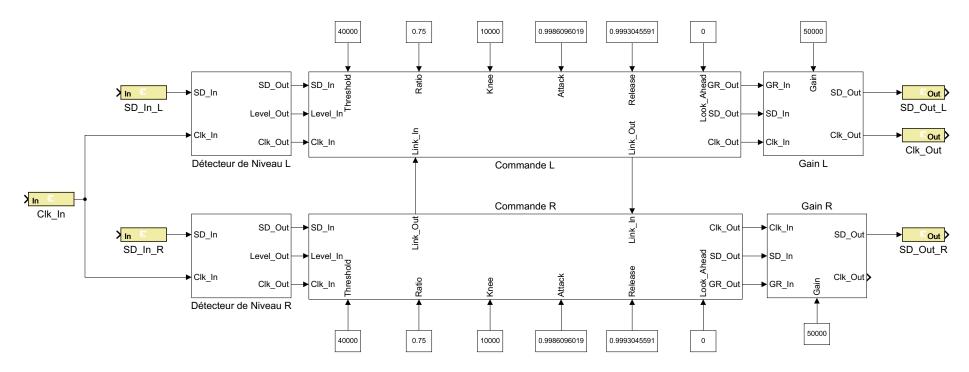

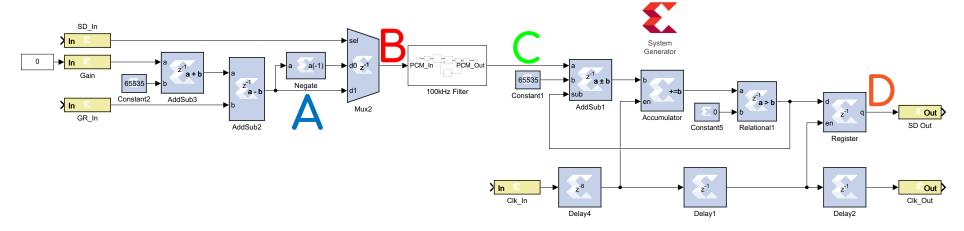

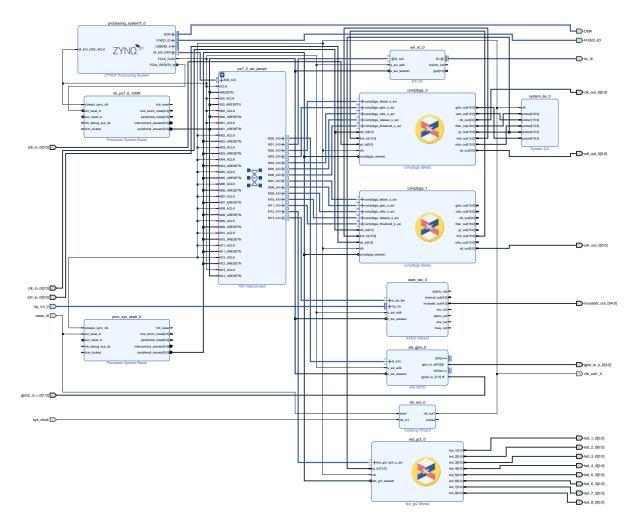

Par souci de compréhension, le compresseur est divisé en trois blocs fonctionnels qui seront présentés successivement (Figure 21).

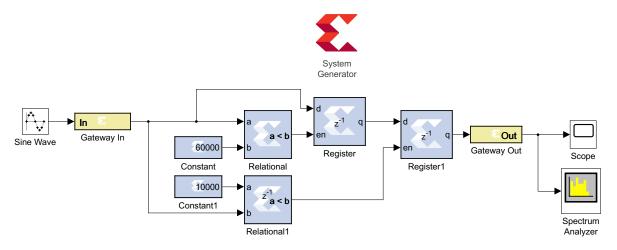

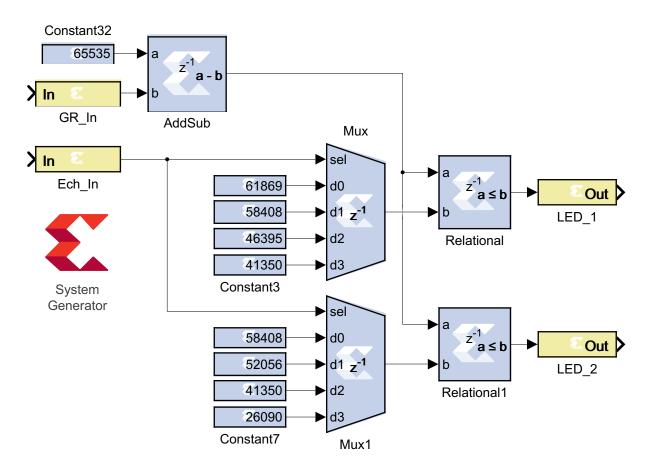

Tous les modèles sont réalisés dans *System Generator for DSP*, nous expliciterons l'utilité de ce programme dans la partie suivante. Nous verrons les modèles comme des schémas fonctionnels, certains blocs seront donc omis par souci de simplicité, car leur présence n'altère pas la compréhension du circuit. Les blocs de fonction utilisés sont définis dans l'annexe A.

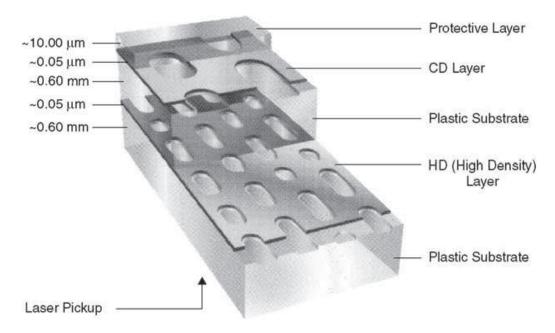

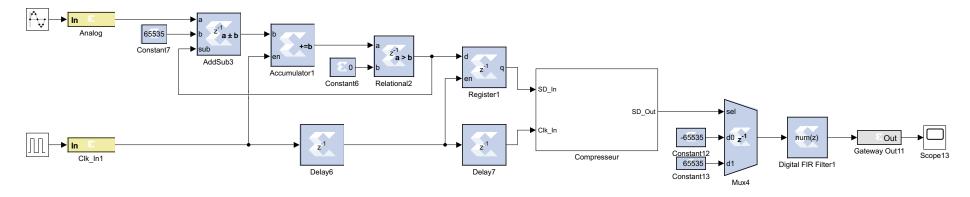

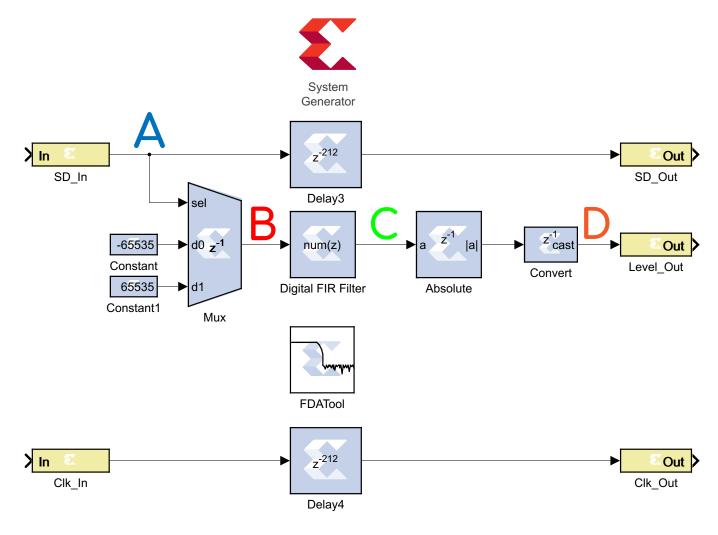

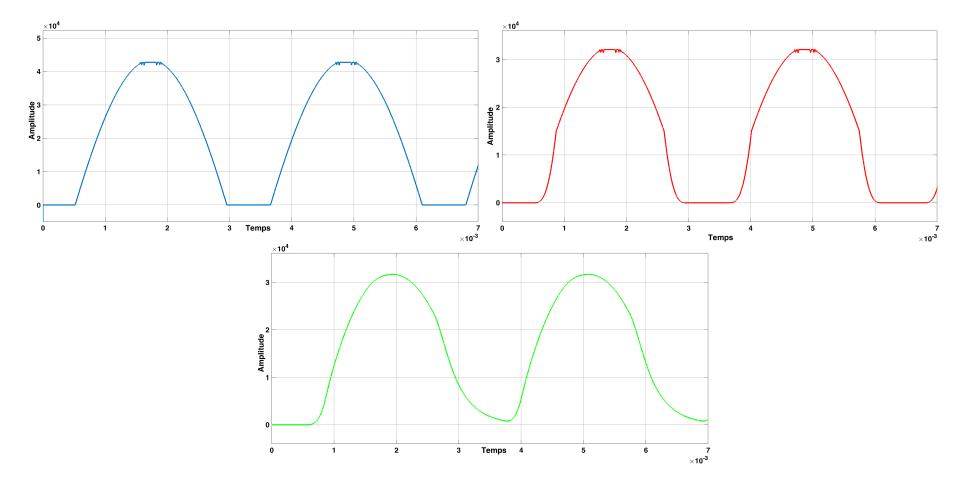

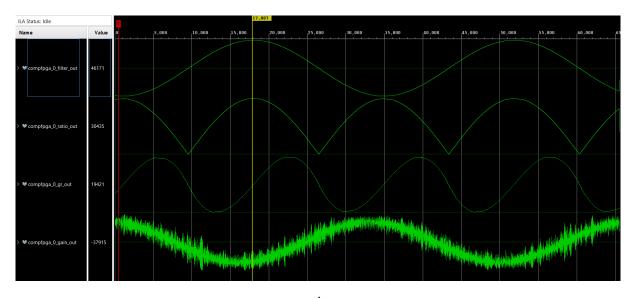

Les graphes de cette partie ont été créés grâce à un modèle de test dans System Generator for DSP (Figure 22). Le signal appliqué à l'entrée du compresseur est un signal sinusoïdal de fréquence 160 Hz et d'amplitude maximale et quantifiée sur 16 bits. Ce sinus est modulé en  $\Sigma/\Delta$  grâce à un  $\Sigma/\Delta$ -M de premier degré. La sortie du compresseur est traitée de la même manière que dans le détecteur de niveau du compresseur (figure 23) afin de récupérer un signal PCM facile à interpréter.

Afin réduire au minimum les artefacts et le bruit de fond engendrés par un simple  $\Sigma/\Delta$ -M de premier ordre, le facteur de suréchantillonnage est augmenté à 256 pour le test du modèle. On pourra tout de même remarquer quelques imprécisions dans la forme d'onde du signal. Ce problème n'apparaîtra normalement pas avec une puce ADC du marché.

Pour visualiser le graphe d'un signal à un moment de son traitement, il suffit de le connecter à un bloc de sortie suivi d'un oscilloscope *Simulink*.

$\frac{\omega}{\omega}$

Figure 21 – Connexion des Trois Blocs pour Réaliser un Compresseur Stéréo dans System Generator for DSP

Figure 22 – Conditions de Test du Compresseur dans System Generator for DSP

$\frac{\omega}{\omega}$

Figure 23 – Modèle System Generator for DSP du Bloc de Détecteur de Niveau

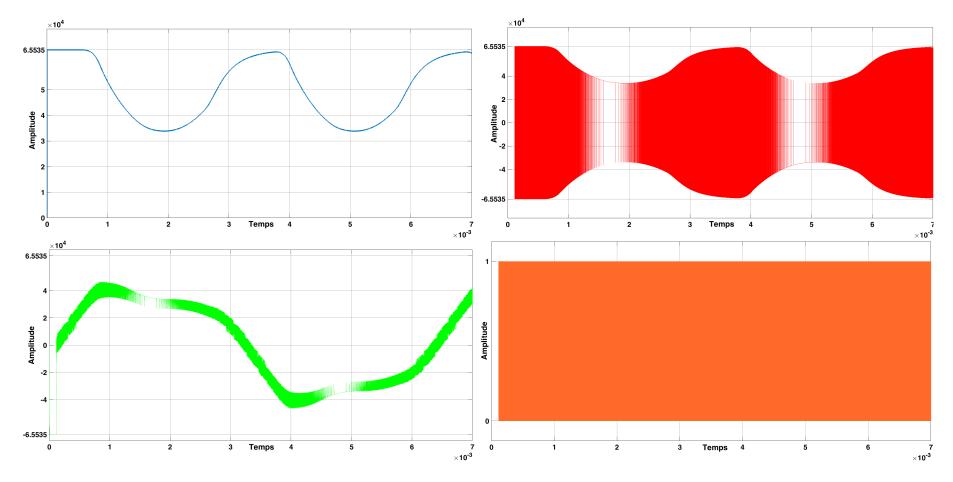

Figure 24 – Signal du Détecteur de Niveau aux Points A (en haut à gauche), B (en haut à droite), C (en bas à gauche) et D (en bas à droite)

#### 3.3.1 Détecteur de Niveau

La première partie du compresseur permet d'évaluer le niveau du signal entrée. Ce procédé est proche d'un convertisseur  $\Sigma/\Delta$  vers PCM. En effet, il est basé autour d'un filtre à réponse impulsionnelle finie ou FIR (Finite Impulse Response).

En premier lieu, les deux blocs d'entrées acheminent le signal  $\Sigma/\Delta$  et le signal d'horloge, provenant de l'ADC, dans le système. Ensuite, l'amplitude du signal  $\Sigma/\Delta$  à 1 bit est étendue à  $\pm 65535$ . Ceci est fait grâce au bloc multiplexeur (Mux) et aux deux blocs de constantes.

Le signal est alors filtré par le bloc FIR configuré par le FDATool. Le filtre est configuré de manière à filtrer le bruit de quantification concentré dans les hautes fréquences et de récupérer un signal de type PCM.

Puis, on récupère la valeur absolue de ce signal PCM. Les crêtes négatives deviennent positives, on a redressé le signal pour récupérer le niveau de crête.

D'après ce calcul simplifié (où le bruit de fond est ignoré, 1 bit = 6 dB), un signal 16 bits non signé nous donne une dynamique de réduction de niveau de 96dB.

$$Dyn = 20log_{10}(2^{16}) \approx 96dB$$

C'est une dynamique bien suffisante pour l'utilisation dans le *sidechain* d'un compresseur. C'est pour cela qu'une amplitude de  $\pm 65535$  a été choisie lors de la première étape. La valeur maximale d'un nombre 16 bits non signé est de 65535. Ainsi, le niveau détecté, une fois redressé (Figure 24 C), à pour maximum 65535. Ce signal peut donc être converti sans pertes par le bloc convertisseur en un nombre non signé exprimé sur 16 bits.

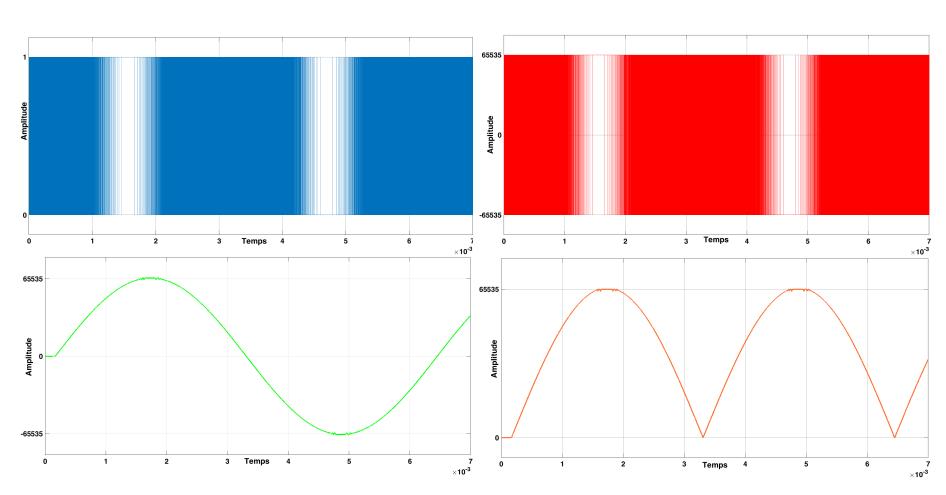

Figure 25 – Modèle System Generator for DSP du Bloc de Commande

Figure 26 – Signal de la Commande aux Points A (en haut à gauche), B (en haut à droite) et C (en bas à gauche)

#### 3.3.2 Section de Commande

Le système de commande reçoit le niveau d'entrée évalué par le détecteur et a pour but de calculer la réduction de gain nécessaire à la compression, en fonction des paramètres qui lui sont donnés. À une exception près, la totalité des contrôles du compresseur s'adresse au système de commande.

La première étape du calcul de réduction de gain est de déterminer si le niveau d'entrée dépasse le seuil de compression. Pour ce faire, on soustrait la valeur du *threshold* au niveau d'entrée. Puis, un bloc de convertisseur convertis le signal en format non signé. Avec la saturation, cela permet de ramener toutes les valeurs négatives à zéro (Figure 26 a).

Ensuite, on multiplie par  $1-\frac{1}{Ratio}$  avec un bloc de multiplication. Le compresseur comprend un knee, le ratio n'est donc pas constant, il dépend du niveau qui dépasse le seuil. On donne en entrée du paramètre de knee la moitié de sa largeur. Le calcul du knee est explicité dans la partie suivante.

On peut tout de même remarquer que le seuil de compression est abaissé de la moitié de la largeur du *knee* car il est nécessaire de commencer à compresser avant le seuil. Les blocs suivants permettent de réaliser le calcul du *knee*.

Après la multiplication par le ratio, le signal de réduction du gain est passé à travers un filtre de premier ordre qui lui donne les caractéristiques d'attaque et de retour (Figure 26 C). Ce filtre est expliqué par la suite. Le coefficient du filtre doit changer en fonction de si le compresseur voit une attaque ou un retour. Pour ce faire, on utilise un bloc de comparaison qui contrôle un multiplexeur avec les coefficients d'attaque et de retour à chaque entrée. On compare entre l'entrée et la sortie du filtre de réponse, l'entrée du filtre peut être vue comme un gain cible et la sortie comme le gain actuel. Si le gain cible est plus bas que le gain actuel, on détecte une attaque. Le contraire est un retour.

Après le filtre de réponse, on envoie le signal de réduction dans une sortie *link*. C'est pour pouvoir coupler ce compresseur mono avec un autre pour avoir un compresseur stéréo (Figure 21). Il y a donc aussi une entrée *link* pour récupérer le signal de réduction du gain d'une autre instance

du compresseur. Pour réaliser la fonction de couplage la plus simple, on choisit le signal de réduction qui présente l'amplitude la plus haute. On présente donc les deux signaux avec un bloc de comparaison qui commande un multiplexeur qui, à son tour, commute entre les deux signaux de réduction de gain.

#### 3.3.3 Knee: Interpolation du Ratio

Le principe d'un *knee* en compression dynamique est d'avoir un ratio de compression qui s'ajuste progressivement avant et après le seuil, en fonction du niveau d'entrée (Figure 18). Le *knee* est donc caractérisé par sa largeur, qui est centrée sur le seuil du compresseur. Cela sous-entend qu'une partie du signal qui n'a pas encore dépassé le seuil de compression est tout de même compressée, mais avec un ratio plus doux. Dans ce modèle, on remédie à cela en soustrayant la moitié de la largeur du *knee* au seuil.

Afin de récupérer les valeurs intermédiaires du ratio, il faut réaliser une interpolation qui connecte les deux extrémités de la largeur du *knee*. On part de la plage dynamique où il n'y a pas de compression jusqu'à la plage dynamique où le ratio est à son maximum (la valeur réglée par l'utilisateur). La façon la plus simple de réaliser une interpolation est de la faire de manière linéaire. On divise le ratio par la largeur du *knee* pour obtenir une augmentation linéaire du ratio sur toute la largeur du *knee*.

On rappelle que, pour notre modèle, on multiplie le signal qui dépasse le seuil de compression par un facteur pour obtenir le signal de réduction du gain de compression. On nommera ce facteur  $R_K$  et voici son expression pour une interpolation linéaire :

$$R_{K1} = \begin{cases} 0 & pour \ x < T - \frac{K}{2} \\ \frac{\left(1 - \frac{1}{R}\right) \cdot x}{K} & pour \ T - \frac{K}{2} < x < T + \frac{K}{2} \\ 1 - \frac{1}{R} & pour \ x > T + \frac{K}{2} \end{cases}$$

Avec x l'amplitude du signal d'entrée avant la soustraction du seuil, R le ratio maximal réglé, T le threshold et K la largeur du knee.

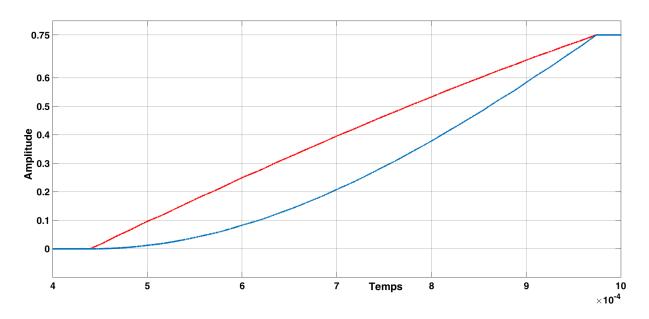

Cependant, à l'instar d'un potentiomètre de volume, pour avoir une réduction de sonie linéaire, il est préférable d'abaisser l'amplitude d'un signal avec une forme logarithmique. Ainsi, il est nécessaire d'employer une interpolation du second degré qui remplace l'évolution du ratio par une section de parabole [Giannoulis, Massberg et Reiss 2012]. L'expression de  $R_K$  devient :

$$R_{K2} = \begin{cases} 0 & pour \ x < T - \frac{K}{2} \\ \frac{\left(1 - \frac{1}{R}\right) \cdot x^2}{K^2} & pour \ T - \frac{K}{2} < x < T + \frac{K}{2} \\ 1 - \frac{1}{R} & pour \ x > T + \frac{K}{2} \end{cases}$$

Figure 27 – Comparaison de l'Interpolation Linéaire (rouge) et l'Interpolation de Deuxième Degrés (bleu) d'un Ratio de Compression de 1 : 4

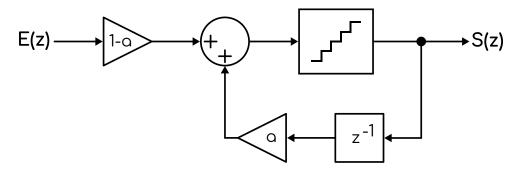

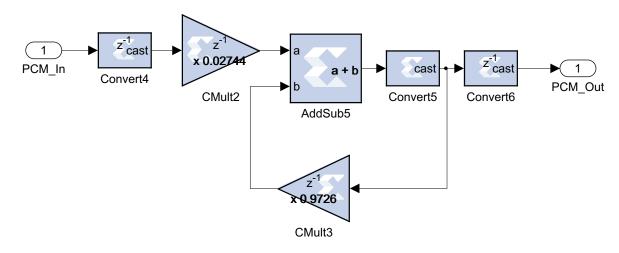

#### 3.3.4 Filtre Passe-Bas du Premier Ordre

#### 3.3.4.1 Calcul du Coefficient

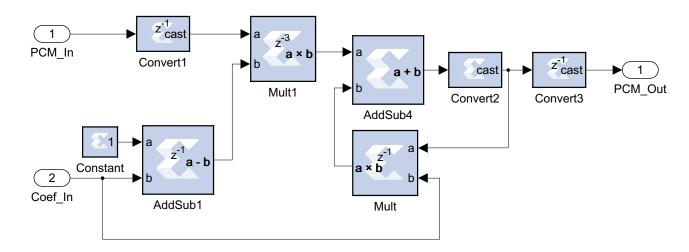

Figure 28 – Schéma d'un Filtre IIR du Premier Ordre en PCM

Faire un filtre à réponse impulsionnelle infinie ou IIR (Infinite Impulse Response), de type passe-bas du premier ordre en PCM, repose sur une boucle de rétroaction et un coefficient a. La figure 28 nous montre que le signal est multiplié par 1-a avant d'être ajouté à la sortie du filtre, qui est retardée d'un échantillon et multipliée par a. Le quantificateur permet de récupérer le même nombre de bits en sortie qu'en entrée.

Le coefficient a doit être inférieur à 1 pour préserver la stabilité du filtre. En effet, avec une boucle de rétroaction positive, une multiplication par un coefficient supérieur à 1 fera tendre la sortie vers l'infini.

Si on linéarise le quantificateur et on ignore le bruit de quantification, on trouve une fonction de transfert :

$$S(z) = E(s) \cdot (1 - a) + a \cdot z^{-1} \cdot S(z) = \frac{E(z) \cdot (1 - a)}{1 - a \cdot z^{-1}}$$

$$H_{LP}(z) = \frac{S(z)}{E(z)} = \frac{1 - a}{1 - a \cdot z^{-1}}$$

Le détail des calculs peut être trouvé dans [Payen de La Garanderie 2015, Annexe 3, p.90-92]. On obtient alors le calcul du coefficient a en fonction de la fréquence de coupure du filtre et de la fréquence d'échantillonnage :

$$a = 2 - \cos\left(\frac{2 \cdot \pi \cdot f_c}{N_0 \cdot F_s}\right) - \sqrt{\left(\cos\left(\frac{2 \cdot \pi \cdot f_c}{N_0 \cdot F_s}\right) - 2\right)^2 - 1}$$

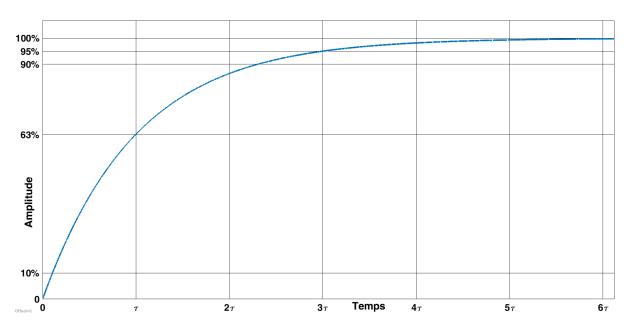

## 3.3.4.2 Temps de Montée

Pour un filtre de réponse de compresseur, ce n'est pas la fréquence de coupure qui nous intéresse, mais le temps de montée. En effet, on veut régler le temps que prend le compresseur à ajuster son gain. Nous allons donc voir quel est le rapport entre la fréquence de coupure d'un filtre de premier ordre et son temps de montée.

Il y a plusieurs façons de qualifier le temps de montée d'un filtre. Dans le cas du compresseur celle qui semble être à privilégier est le temps de montée jusqu'à 63 % de la valeur du régime permanent. Néanmoins, beaucoup de compresseurs ne calculent pas le temps de montée de cette façon. Il n'est pas rare de voir le temps de montée de 10 à 90 % ou le temps de compresser un nombre de décibels arbitraire.

Le temps de montée est mise en évidence par la sortie du filtre quand un échelon est appliqué en entrée; cela s'appelle la réponse indicielle. La constante de temps  $\tau$  correspond au temps de montée de 63 %;  $\tau$  est égal à l'inverse de la pulsation de coupure  $\omega_c$ . On a donc :

$$\tau = t_{63\%} = \frac{1}{\omega_c} = \frac{1}{2 \cdot \pi \cdot f_c} \approx \frac{0.16}{f_c}$$

On peut s'intéresser au temps de montée de 10 à 90 % qui est égal à  $2, 2 \cdot \tau$ . Pour un temps total de montée, on peut considérer que le régime permanent est atteint au bout de  $5 \cdot \tau$ . On peut les exprimer facilement en fonction de la fréquence de coupure :

$$t_{10\% \to 90\%} = 2, 2 \cdot \tau = \frac{2, 2}{\omega_c} = \frac{2, 2}{2 \cdot \pi \cdot f_c} \approx \frac{0, 35}{f_c}$$

$$t_{total} = 5 \cdot \tau = \frac{5}{\omega_c} = \frac{5}{2 \cdot \pi \cdot f_c} \approx \frac{0, 8}{f_c}$$

Figure 29 – Réponse Indicielle du Modèle de Filtre Passe-Bas Réalisé dans System Generator for DSP

#### 3.3.4.3 Modèle du Filtre

Pour réaliser le filtre de premier ordre dans *System Generator for DSP* on peut s'inspirer directement de la figure 28. Un bloc de conversion sert de quantificateur.

Il faut faire attention à la gestion des retards et faire en sorte qu'il y ai un retard d'un échantillon dans la boucle de contre-réaction, mais pas de retard dans les blocs d'addition et de quantification.

Comme on doit multiplier la valeur des échantillons du signal d'entrée par des coefficients précis, on effectue tous les calculs en virgule flottante (simple précision). Le bloc de conversion en entrée est utilisé pour convertir le signal 16 bits virgule fixe non-signé en *float*. Le bloc de conversion de sortie fait l'opération contraire.

Avec les différents blocs de multiplication, on peut faire une version du filtre avec coefficient constant et un autre avec un coefficient variable.

Figure 30 – Modèle System Generator for DSP du Filtre Passe-Bas PCM du Premier Ordre à Coefficient Variable

Figure 31 – Modèle System Generator for DSP du Filtre Passe-Bas PCM du Premier Ordre à Coefficient Fixe

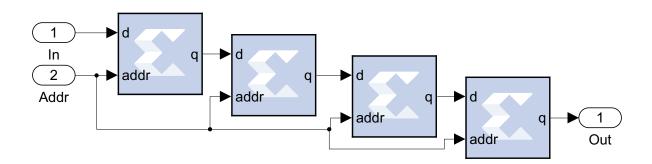

#### 3.3.5 Ligne à Retard du Look-Ahead

La fonction *look-ahead* d'un compresseur repose sur le fait d'introduire un retard au signal à traiter par rapport au signal détecté du *sidechain* afin d'avoir un compresseur qui "voit" les changements dynamiques en avance.

Dans un système numérique, une ligne à retard variable sous-entend une mémoire tampon à longueur réglable. Le bloc de registre adressable est une mémoire à longueur variable avec un maximum de 1024 bits. En se référant à d'autres compresseurs avec *look-ahead*, il semble qu'un maximum de délai de 10 ms est suffisant. 10 ms d'audio en DSD128 représente une mémoire de :

$$Nb_{10ms} = 128 \cdot 44\,100 \cdot 1 \cdot 10 \cdot 10^{-3} = 56\,448\,bits$$

En divisant ce nombre par 1024, on trouve que 55 blocs de mémoire sont suffisants pour stocker environ 10 ms d'audio  $\Sigma/\Delta$ . Il suffit alors de les relier en série et de transmettre la même adresse de mémoire à tous les blocs. Ainsi, chaque incrémentation de l'adresse entraînera 55 bits de retard (ce qui correspond à environ 9,5  $\mu$ s).

Figure 32 – Modèle Réduit de la Ligne à Retard dans System Generator for DSP

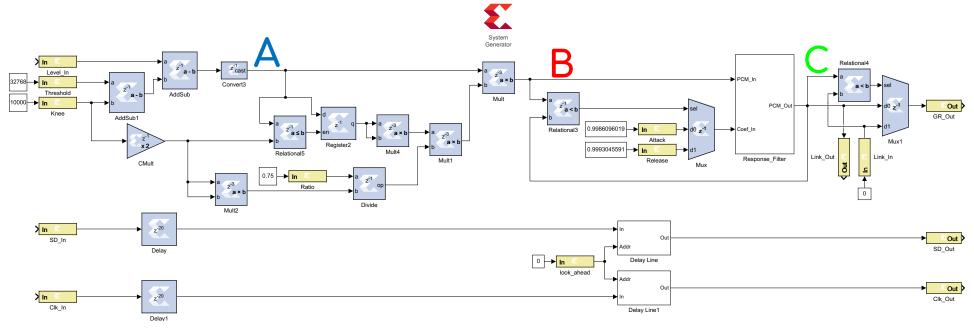

Figure 33 – Modèle System Generator for DSP du Bloc de Gain

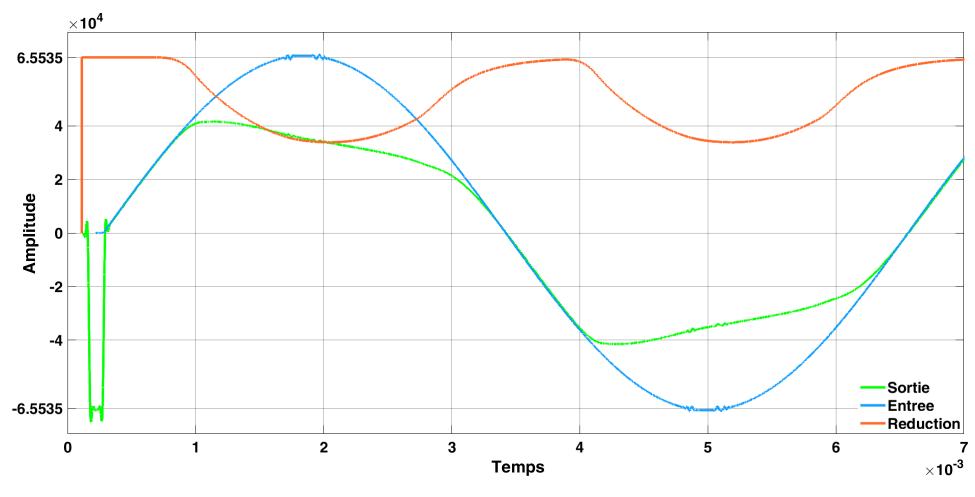

Figure 34 – Signal du Gain aux Points A (en haut à gauche), B (en haut à droite), C (en bas à gauche) et D (en bas à droite)

#### 3.3.6 Module de Gain

Une fois que le niveau de réduction appropriée est calculé, il faut l'appliquer comme gain au flux  $\Sigma/\Delta$ .

On commence par soustraire le signal de réduction, calculé dans le système de commande, au gain maximum qu'on souhaite avoir. Ici, le gain maximum souhaité est 65535 (gain unitaire) plus un *make-up gain* choisi par l'utilisateur (Figure 34 A).

Pour appliquer le gain, on donne l'amplitude de  $\pm$ Gain au signal  $\Sigma/\Delta$  (Figure 34 B). On réalise cette opération avec un bloc multiplexeur et un bloc de négation. Avec une amplitude maximale de  $\pm 65535$ , le signal est alors codé sur 17 bits signé.

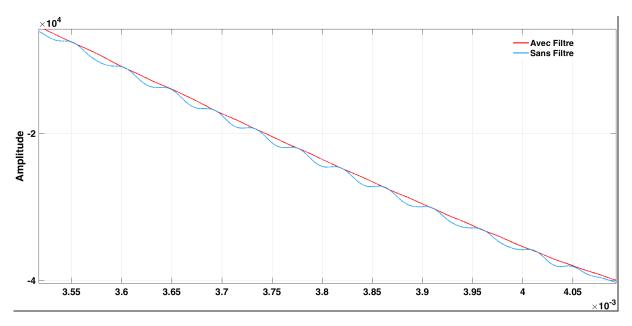

Pour récupérer un signal sur 1 bit, il faut utiliser un modulateur  $\Sigma/\Delta$ . Au préalable, on fait passer le signal multi bit dans un filtre de premier ordre (Figure 31) avec une fréquence de coupure de 100 kHz. Le rôle de ce filtre est de stabiliser le  $\Sigma/\Delta$ -M. En effet, si on injecte un signal de fréquence trop élevée dans le  $\Sigma/\Delta$ -M cela engendre des distorsions, comme mit en évidence dans la figure 35.

Figure 35 – Comparaison du Signal de Sortie Avec et Sans le Filtre Précédent le Modulateur  $\Sigma/\Delta$

La saturation du format à virgule fixe signé 17 bits fait en sorte que la sortie du filtre ne peut pas être supérieure à  $\pm 65535$ . Ainsi, même si l'on donne un gain de compensation très fort en entrée, la saturation limitera l'amplitude du signal d'entrée du  $\Sigma/\Delta$ -M. Ceci est important, car un  $\Sigma/\Delta$ -M

basique pourrait facilement se déstabiliser avec une amplitude d'entrée trop grande. Il est donc préférable de saturer en entrée.

Une fois filtré, on entre donc dans un modulateur  $\Sigma/\Delta$  d'ordre 1. Le premier bloc d'addition-soustraction est équivalent à adapter l'amplitude de la sortie 1 bit à celle de l'entrée et de la soustraire à l'entrée. Quand la sortie du modulateur est 1, on soustrait le maximum de l'amplitude d'entrée (65535) au signal d'entrée. Quand la sortie du modulateur est 0 on soustrait le minimum de l'amplitude d'entrée (-65535), ce qui revient à ajouter 65535.

Le bloc suivant accumule l'erreur de quantification résultante. L'entrée enable permet de s'assurer que l'accumulation est faite de manière synchrone afin d'avoir une valeur d'erreur de quantification accumulée par échantillon.

Le bloc *relational* à la suite vérifie si l'erreur accumulée est supérieure à 0, ce qui donne un flux  $\Sigma/\Delta$  en sortie. Le bloc *register* en sortie est ajouté pour s'assurer que le flux  $\Sigma/\Delta$  est transmis de manière synchrone.

Antoine Ricoux

Figure 36 – Comparaison du Signal de Détecté, du Signal de Sortie Compressé et du Signal de Réduction de Gain (le Délai est Compensé)

# 4 Réalisation du Compresseur Sigma-Delta sur SoC

## 4.1 Architecture d'un Système sur Puce

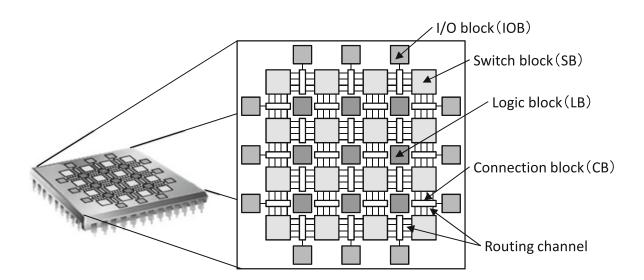

#### 4.1.1 Architecture de Base d'un FPGA

L'un des points forts d'un FPGA est le fait que son circuit peut être reconfiguré entièrement en quelques secondes, pour passer d'une fonction à une autre. La majorité des fabricants choisissent la technologie de mémoire vive statique ou SRAM (Static Random Access Memory) pour stocker le programme du FPGA. L'avantage de la SRAM est sa rapidité, le nombre illimité de programmations et sa place réduite sur la puce [Pang et Membrey 2017]. Le principal désavantage vient du fait que c'est une mémoire volatile, ce qui veut dire que le programme du FPGA doit être chargé dans la SRAM depuis une mémoire non volatile au moment de la mise en route. C'est un procédé lent par rapport à une puce programmée dans une mémoire non volatile. La plupart des FPGA possèdent donc une mémoire à lecture seule effaçable électriquement ou EEPROM (Electrically-Erasable Programmable Read-Only Memory) qui est prévue pour charger la mémoire vive au démarrage.

Il existe d'autres technologies de programmation que la SRAM, comme la mémoire Flash ou Antifuse qui sont non-volatile. Mais elles n'égalent pas la performance de la SRAM et sont utilisées dans des contextes spécifiques.

Figure 37 – Architecture Classique "en Îles" d'un FPGA [Amano 2018, Firgure 2.1, p.24]

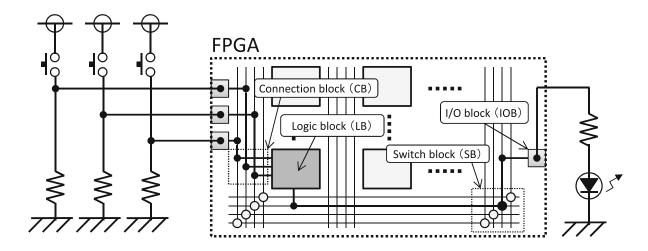

L'architecture d'un FPGA repose sur quatre blocs élémentaires :

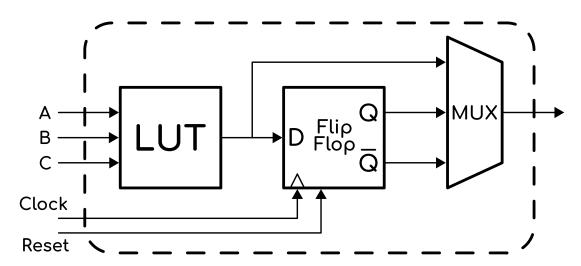

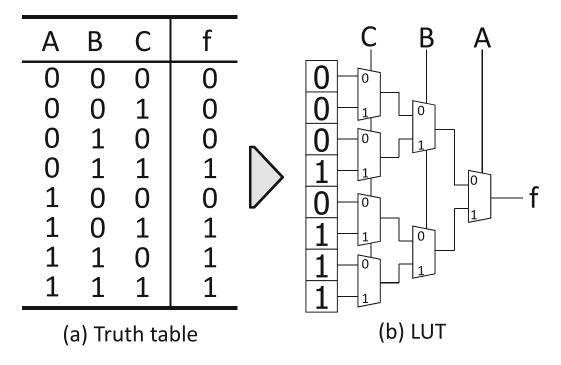

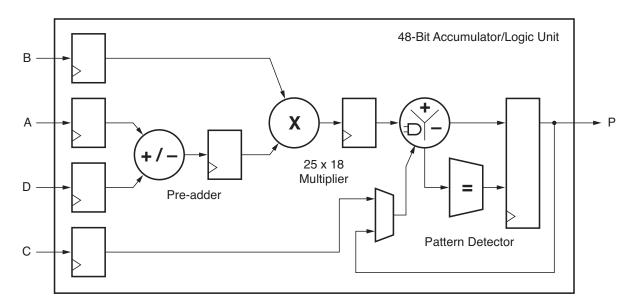

- Le bloc logique ou LB (Logic Block): C'est une porte logique programmable dont l'élément principal est une table de correspondance ou LUT (Look-Up Table). D'autres éléments peuvent être présents, comme un circuit de bascule pour pouvoir synchroniser le bloc à une horloge, ou un multiplexeur pour choisir le signal à présenter en sortie (Figure 38).

- Le bloc d'entrée/sortie ou IOB (Input/Output Block): C'est le bloc responsable de gérer les connexions entre le circuit interne et les broches de la puce. Ils sont aussi chargés de configurer chaque broche comme une entrée ou une sortie ainsi que de connecter des résistances entre l'alimentation et la broche si nécessaire.

- Le bloc de connexion ou CB (*Connection Block*): Ce sont des connexions qui sont chargées de relier les LB entre eux et avec les IOB.

- Le bloc commutateur ou SB (Switch Block): Les SB sont des commutateurs programmables qui servent à acheminer les signaux aux bons endroits. Ce sont eux qui gèrent toutes les connexions faites par les CB.

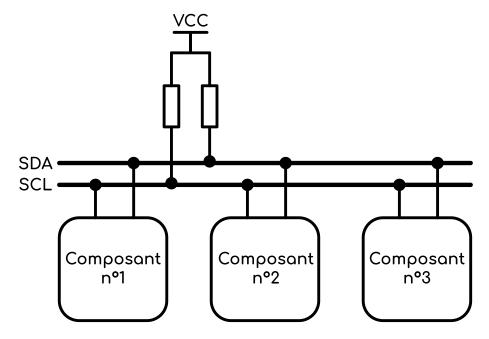

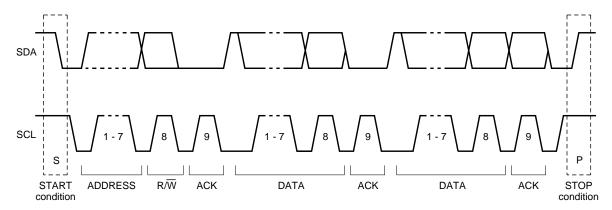

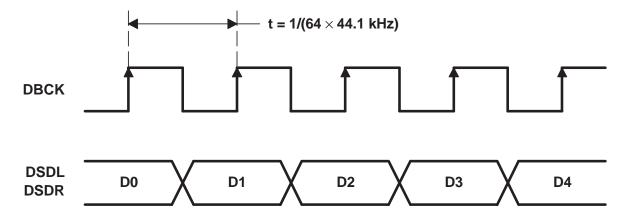

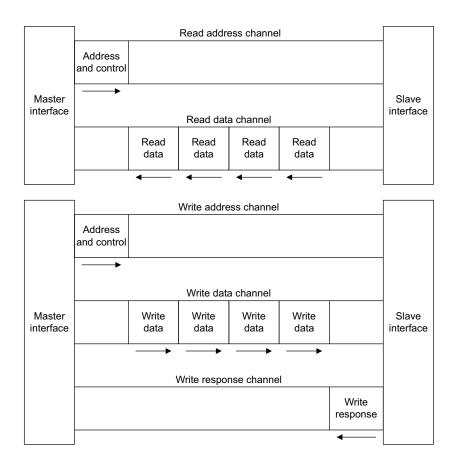

Figure 38 – Schéma Simplifié d'un Bloc Logique [d'après Pang et Membrey 2017, Figure 1.2, p.5]